## SYNTHESIS OF SPECIFICATIONS AND REFINEMENT MAPS FOR REAL-TIME OBJECT CODE VERIFICATION

A Dissertation

Submitted to the Graduate Faculty

of the

North Dakota State University

of Agriculture and Applied Science

By

Eman Mohammad Al-Qtiemat

In Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY

Major Department: Electrical and Computer Engineering

April 2020

Fargo, North Dakota

#### NORTH DAKOTA STATE UNIVERSITY

Graduate School

#### Title

### SYNTHESIS OF SPECIFICATIONS AND REFINEMENT MAPS FOR DEAL TIME ODIECT CODE VEDIEICATION

| REAL-TIME OBJECT CODE VERIFICATION |  |

|------------------------------------|--|

| By                                 |  |

| Eman Mohammad Al-Qtiemat           |  |

The supervisory committee certifies that this dissertation complies with North Dakota State University's regulations and meets the accepted standards for the degree of

#### DOCTOR OF PHILOSOPHY

## SUPERVISORY COMMITTEE: Dr.Sudarshan Srinivasan Dr.Danling Wang Dr. Yechun Wang Dr.Dharmakeerthi Nawarathna Approved: Ben Braaten 26, April, 2020 Department Chair

Date

#### ABSTRACT

Formal verification methods have been shown to be very effective in finding corner-case bugs and ensuring the safety of embedded software systems. The use of formal verification requires a specification, which is typically a high-level mathematical model that defines the correct behavior of the system to be verified. However, embedded software requirements are typically described in natural language. Transforming these requirements into formal specifications is currently a big gap. While there is some work in this area, we proposed solutions to address this gap in the context of refinement-based verification, a class of formal methods that have shown to be effective for embedded object code verification. The proposed approach also addresses both functional and timing requirements and has been demonstrated in the context of safety requirements for software control of infusion pumps. The next step in the verification process is to develop the refinement map, which is a mapping function that can relate an implementation state (in this context, the state of the object code program to be verified) with the specification state. Actually, constructing refinement maps often requires deep understanding and intuitions about the specification and implementation, it is shown very difficult to construct refinement maps manually. To go over this obstacle, the construction of refinement maps should be automated. As a first step toward the automation process, we manually developed refinement maps for various safety properties concerning the software control operation of infusion pumps. In addition, we identified possible generic templates for the construction of refinement maps. Recently, synthesizing procedures of refinement maps for functional and timing specifications are proposed. The proposed work develops a process that significantly increases the automation in the generation of these refinement maps. The refinement maps can then be used for refinement-based verification. This automation procedure has been successfully applied on the transformed safety requirements in the first part of our work. This approach is based on the identified generic refinement map templates which can be increased in the future as the application required.

#### ACKNOWLEDGEMENTS

All praises and thanks to Allah almighty, my Creator, my Sustainer, for giving me courage and strength to pursue my PhD and fulfill the requirements of this disquisition.

My heartiest and sincere appreciation and gratitude to my mentor and adviser Dr. Sudarshan Srinivasan, who always encouraged me, and persistently conveyed the spirit and guidance required for the research. Without his kind guidance and continuous efforts, this disquisition would not have been possible.

Special thanks to my committee members, Dr. Danling Wang, Dr. Yechun Wang, Dr. Scott Smith and Dr. Dharmakeerthi Nawarathna for their support, guidance and helpful recommendations. Thanks to the Electrical and Computer Engineering staff members for all the unconditional help and favor. I owe my heartiest thanks to all my friends and colleagues here in the US and Jordan, who always helped me in the time of need. I am grateful to the United States Agency for International Development (USAID) Government for the financial support that I have received as a graduate student. Getting funding for the most part of my Ph.D. journey has helped reduced the constant worry of supporting myself financially.

I would like to thank my beloved family, each one of you has contributed to helping me become the person I am today. A special thanks to my husband 'Zeyad' who has been through the various ups and downs of our life together during my Ph.D. journey. He has indeed taught me a different aspect of seeing life. He has been through all my tantrums and still supported me in achieving this goal. He supported me in many ways. Thank you for coming into my life. Also, I would like to thank my sons Adam and Karam, for their patience, time, and support as you both are the source of happiness for me. Today, as I fulfill my dad's and mum's dream who have supported me emotionally throughout this challenging time. Your motivational words have helped me to survive this big journey of Ph.D. A Special thanks to you as you are the only and every reason for whatever I am today and whatever I achieved in my life.

My brothers, sisters, and your beloved kids, your continuous support is always a source of motivation and encouragement for me. Thank you for you all and your families as well. I would like to thank my Friends who have supported me and believed in my abilities to do such work, i am lucky to have you in my life. Thank you each and everyone for your encouraging words whenever I needed them the most. Without all of your support, I would not have come this far and achieved all this.

"Do [as you will], for Allah will see your deeds, and [so, will] His Messenger and the believers. And you will be returned to the Knower of the unseen and the witnessed, and He will inform you of what you used to do." Holly Quran, surah At Taubah, chapter 9, verse 105.

<sup>&</sup>quot;And the last of our call will be, Praise to Allah, Lord of the worlds!"

## **DEDICATION**

I would like to dedicate this dissertation to my family, especially to my parents, my husband, and my sons (Adam and Karam) for all the love, support, and motivation.

## TABLE OF CONTENTS

| A  | BSTR | CAC'T  |                                                       | iii  |

|----|------|--------|-------------------------------------------------------|------|

| A  | CKNO | OWLEI  | GEMENTS                                               | iv   |

| D] | EDIC | ATION  |                                                       | vi   |

| LI | ST O | F TAB  | ES                                                    | Х    |

| LI | ST O | F FIGU | RES                                                   | xi   |

| LI | ST O | F APP  | ENDIX TABLES                                          | xiii |

| LI | ST O | F APP  | ENDIX FIGURES                                         | xiv  |

| 1  | INT  | RODU   | TION                                                  | 1    |

|    | 1.1  | Overv  | PW                                                    | 1    |

|    | 1.2  | Motiv  | tion                                                  | 1    |

|    | 1.3  | Proble | n Statement                                           | 2    |

|    |      | 1.3.1  | Testing                                               | 2    |

|    |      | 1.3.2  | Formal Verification                                   | 3    |

|    | 1.4  | Thesis | Outline                                               | 6    |

|    | 1.5  | Refere | ices                                                  | 7    |

| 2  |      |        | OF FORMAL SPECIFICATIONS FROM REQUIREMENTS FOR RE-    |      |

|    | FIN  | EMEN'  | BASED REAL TIME OBJECT CODE VERIFICATION              | 10   |

|    | 2.1  | Introd | ction                                                 | 10   |

|    | 2.2  | Backg  | ound                                                  | 12   |

|    |      | 2.2.1  | Parsing Tree                                          | 12   |

|    |      | 2.2.2  | Transition Systems                                    | 13   |

|    |      | 2.2.3  | Timed Transition Systems                              | 14   |

|    | 2.3  | Relate | l Work                                                | 14   |

|    | 2.4  | Forma  | Model Synthesis Procedure for Functional Requirements | 17   |

|    |      | 2.4.1  | Atomic Proposition Extraction Rule 1 (APER 1)         | 17   |

|   |     | 2.4.2  | Atomic Proposition Extraction Rule 2 (APER 2)                                                              | 19 |

|---|-----|--------|------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.4.3  | Atomic Proposition Extraction Rule 3 (APER 3)                                                              | 22 |

|   |     | 2.4.4  | High-Level Procedure for Specification Transition System Synthesis                                         | 24 |

|   | 2.5 | Forma  | l Model Synthesis Procedure for Timing Requirements                                                        | 26 |

|   |     | 2.5.1  | Atomic Proposition and Timing Constrains Extraction Rule (APTCER) for Timed Transition System              | 26 |

|   |     | 2.5.2  | $\label{thm:condition} \mbox{High-Level Procedure for Specification Timed Transition System Synthesis}  .$ | 28 |

|   | 2.6 | Case S | Study: Generic Insulin Infusion Pump (GIIP)                                                                | 31 |

|   |     | 2.6.1  | Functional Requirements of GIIP                                                                            | 31 |

|   |     | 2.6.2  | Timing Requirements of GIIP                                                                                | 32 |

|   | 2.7 | Result | s Analysis                                                                                                 | 37 |

|   | 2.8 | Conclu | usion                                                                                                      | 40 |

|   | 2.9 | Refere | ences                                                                                                      | 41 |

| 3 |     |        | S OF REFINEMENT MAPS FOR REAL-TIME OBJECT CODE VERIFI-                                                     | 45 |

|   | 3.1 | Introd | uction                                                                                                     | 45 |

|   | 3.2 | Backg  | round                                                                                                      | 46 |

|   |     | 3.2.1  | Transition Systems                                                                                         | 46 |

|   |     | 3.2.2  | Timing Transition Systems                                                                                  | 47 |

|   |     | 3.2.3  | Refinement-Based Verification                                                                              | 48 |

|   |     | 3.2.4  | Synthesis of Functional Formal Specifications                                                              | 49 |

|   |     | 3.2.5  | Synthesis of Timing Formal Specifications                                                                  | 49 |

|   | 3.3 | Relate | ed Work                                                                                                    | 52 |

|   | 3.4 | Refine | ment Maps and Refinement Map Templates                                                                     | 55 |

|   | 3.5 | Synthe | esis of Refinement Maps for System Requirements                                                            | 62 |

|   | 3.6 | Conclu | usion and Future Work                                                                                      | 67 |

|   | 3 7 | Refere | ences                                                                                                      | 67 |

| 4  | COI  | NCLUSIONS AND FUTURE WORK                                | 72 |

|----|------|----------------------------------------------------------|----|

|    | 4.1  | Conclusions                                              | 72 |

|    | 4.2  | Directions for Future Research                           | 73 |

| Al | PPEN | NDIX A. INSULIN PUMP SAFETY REQUIREMENTS                 | 75 |

| Al | PPEN | NDIX B. PARSED TREES OF INSULIN PUMP SAFETY REQUIREMENTS | 78 |

| Al | PPEN | IDIX C. LIST OF PUBLICATIONS                             | 97 |

## LIST OF TABLES

| Tab. | <u>le</u>                                                                                             | Pag | ge            |

|------|-------------------------------------------------------------------------------------------------------|-----|---------------|

| 2.1  | AP-Truth table for requirements 1.8.2 and 1.8.5 from AP-list                                          | . : | 32            |

| 2.2  | Resulting transition systems by applying procedure 4 and APERS on a set of system requirements        |     | 35            |

| 2.3  | AP-truth-table for timing requirement 1.6.1 from AP-list                                              | . : | 36            |

| 2.4  | Resulting timed transition systems by applying procedure 6 and APTCER on a set of timing requirements |     | 39            |

| 3.1  | List of abbreviations for Figures 3.6-3.15                                                            | . ( | <sub>35</sub> |

## LIST OF FIGURES

| Figu | <u>re</u>                                                                                                       | Page |

|------|-----------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Integrating safety requirements into software development life cycle                                            | . 3  |

| 1.2  | Requirement 1.1.1 in both natural language and formal forms                                                     | . 5  |

| 2.1  | A simple example of a parsing tree using Enju parser                                                            | . 13 |

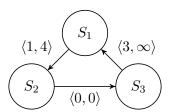

| 2.2  | An example of a transition system (TS)                                                                          | . 13 |

| 2.3  | An example of a timed transition system (TTS)                                                                   | . 14 |

| 2.4  | An Enju parsing tree portion shows some resulting APs by applying APER 1                                        | . 18 |

| 2.5  | An Enju parsing tree portion of requirement 2.2.2 shows some resulting APs by applying APER 1                   | . 19 |

| 2.6  | An Enju parsing tree portion of requirement 1.8.2 shows some resulting APs by applying APER 1                   | . 20 |

| 2.7  | An Enju parsing tree portion of requirement 1.2.6 shows some resulting APs by applying APER 2                   | . 21 |

| 2.8  | An Enju parsing tree portion shows some resulting APs by applying APER 2                                        | . 22 |

| 2.9  | An Enju parsing tree portion shows some resulting APs by applying APER 2 on requirement 1.1.3                   | . 23 |

| 2.10 | An Enju parsing tree portion shows some resulting APs using APER 3                                              | . 25 |

| 2.11 | An Enju parsing tree portion shows some resulting APs by applying APER 3 on requirement 3.2.5.                  | . 26 |

| 2.12 | An Enju parsing tree shows three resulting TBSs after applying APTCER                                           | . 33 |

| 2.13 | An Enju parsing tree portion shows the resulting TBS $\langle AP-list, TC-list \rangle$ ) after applying APTCER | . 34 |

| 2.14 | Finite state machine for suspension mode requirements (1.8.1 and 1.8.5)                                         | . 37 |

| 2.15 | Timed finite state machine for air-in-line requirement $(1.6.1)$                                                | . 38 |

| 3.1  | An example of a transition system (TS)                                                                          | . 47 |

| 3.2  | An example of a timing transition system (TTS)                                                                  | . 48 |

| 3.3  | Flowchart of formal model synthesis procedure for Functional Requirements. $\dots$                              | . 50 |

| 3.4  | Flowchart of formal model synthesis procedure for Timing Requirements                                           | . 51 |

| 3.5  | A formal presentation of requirement 1.1.1 and the suggested refinement maps                    | 55 |

|------|-------------------------------------------------------------------------------------------------|----|

| 3.6  | A formal presentation of requirement 1.1.3 and the suggested refinement maps                    | 56 |

| 3.7  | A formal presentation of requirement $1.8.2$ and $1.8.5$ and the suggested refinement maps.     | 56 |

| 3.8  | A formal presentation of requirement 1.3.5 and the suggested refinement maps                    | 57 |

| 3.9  | A formal presentation of requirement $2.2.2$ and $2.2.3$ and the suggested refinement maps.     | 57 |

| 3.10 | A formal presentation of requirement $3.2.5$ followed by the suggested refinement maps          | 58 |

| 3.11 | A formal presentation of requirement $3.2.7$ followed by the suggested refinement maps          | 58 |

| 3.12 | A formal presentation of the timing requirement $1.2.8$ and the suggested refinement maps.      | 59 |

| 3.13 | A formal presentation of the timing requirement 1.6.1 followed by the suggested refinement maps | 59 |

| 3.14 | A formal presentation of the timing requirement 1.8.4 followed by the suggested refinement maps | 60 |

| 3.15 | A formal presentation of the timing requirement 2.2.1 followed by the suggested refinement maps | 60 |

## LIST OF APPENDIX TABLES

| Tabl | $\underline{le}$                                 | ] | Page |

|------|--------------------------------------------------|---|------|

| B.1  | The main syntactic categories used by Enju trees |   | 78   |

## LIST OF APPENDIX FIGURES

| Figu | $\phantom{aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa$    | Page |

|------|---------------------------------------------------|------|

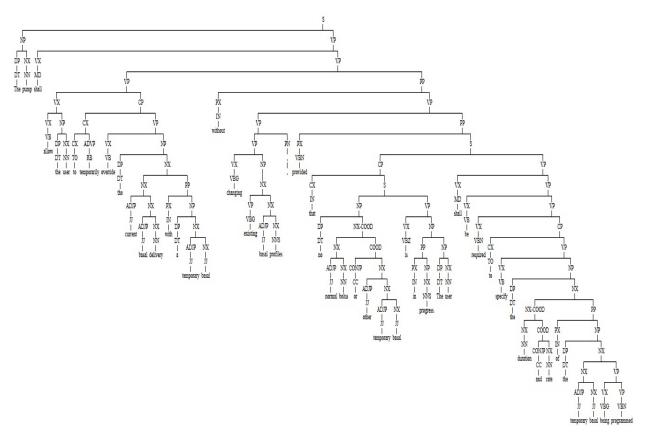

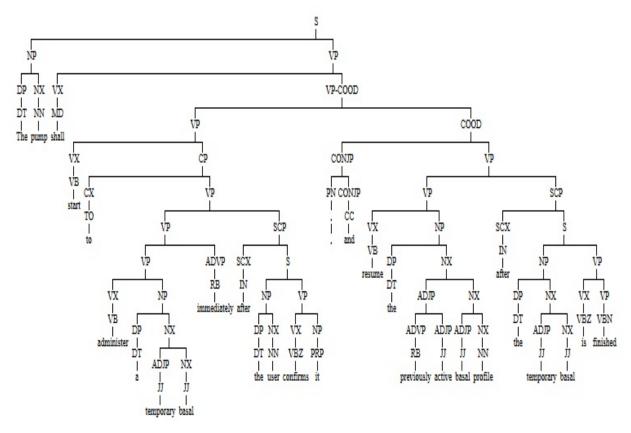

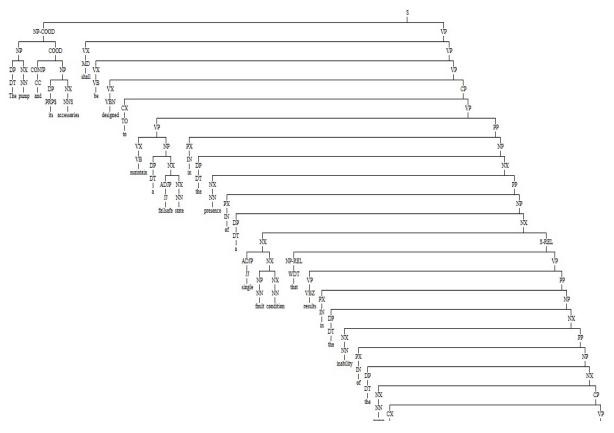

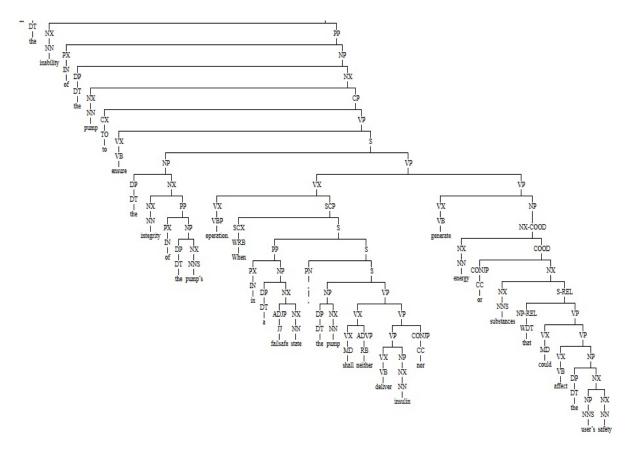

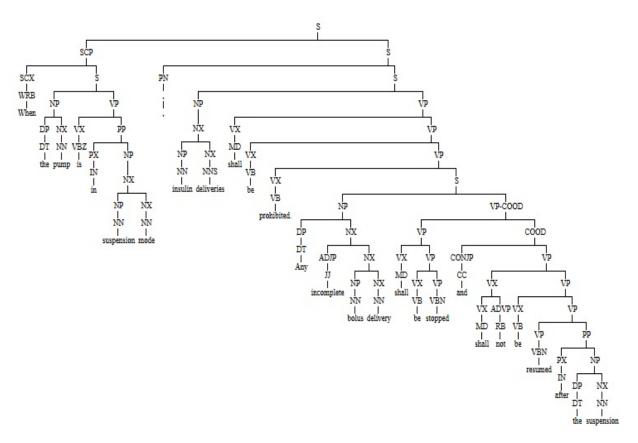

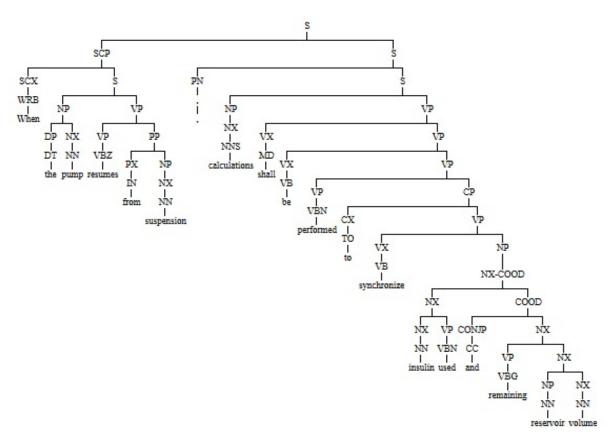

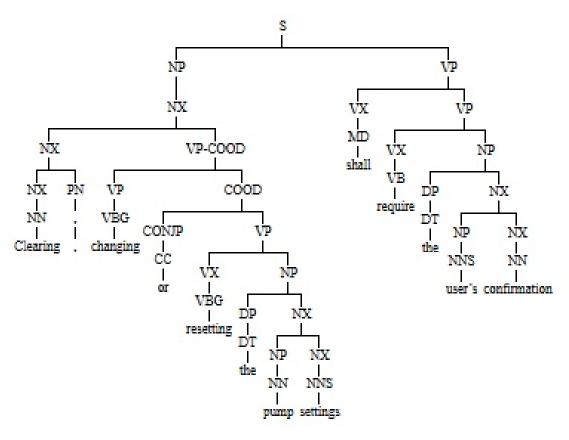

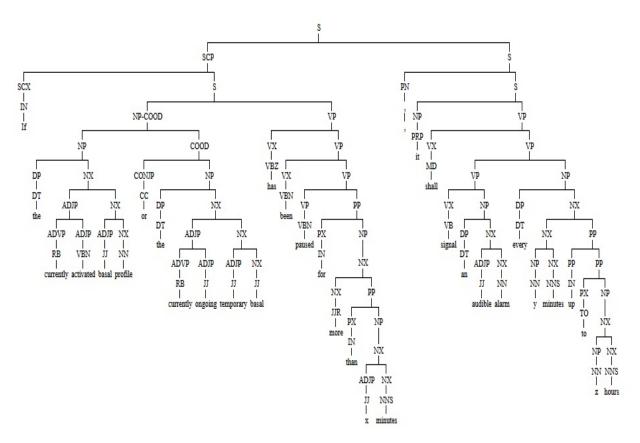

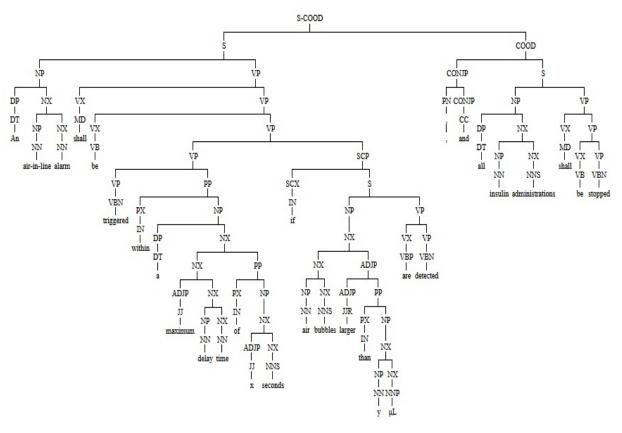

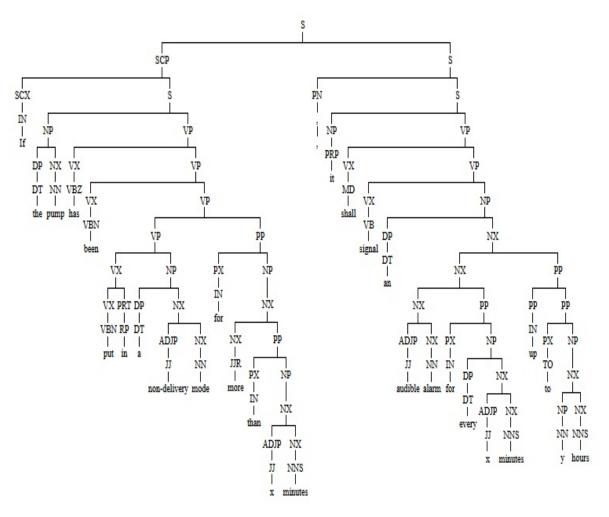

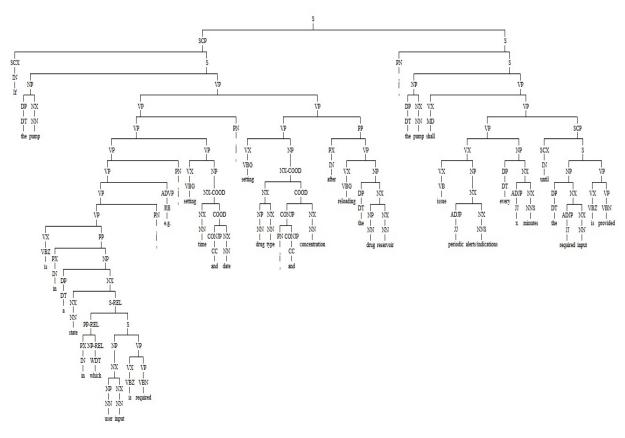

| B.1  | Enju parsed tree for requirement 1.1.1            | 79   |

| B.2  | Enju parsed tree for requirement 1.1.3            | . 80 |

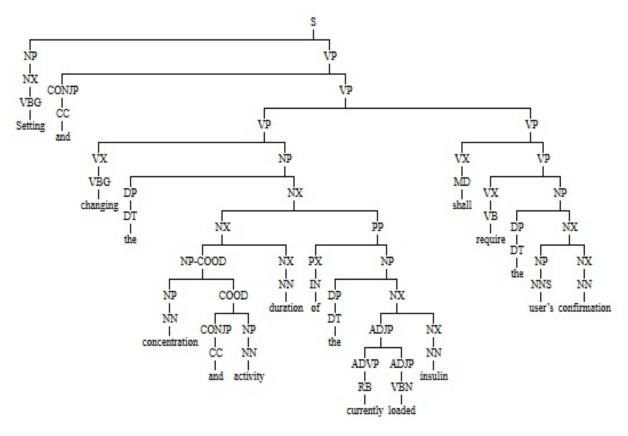

| В.3  | Enju parsed tree for requirement 1.2.4            | 81   |

| B.4  | Enju parsed tree for requirement 1.2.6            | . 82 |

| B.5  | Enju parsed tree for requirement 1.2.7            | 83   |

| B.6  | Enju parsed tree for requirement 1.3.5            | . 84 |

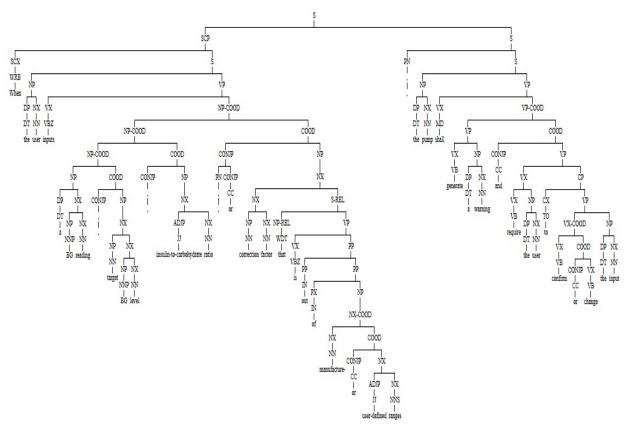

| B.7  | Enju parsed tree for requirement 3.1.1 (part one) | . 85 |

| B.8  | Enju parsed tree for requirement 3.1.1 (part two) | . 86 |

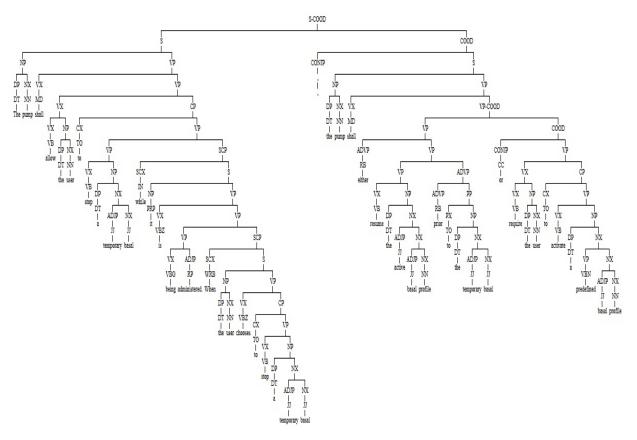

| B.9  | Enju parsed tree for requirement 1.8.2            | . 87 |

| B.10 | Enju parsed tree for requirement 1.8.5            | . 88 |

| B.11 | Enju parsed tree for requirement 2.2.2            | . 89 |

| B.12 | Enju parsed tree for requirement 2.2.3            | 90   |

| B.13 | Enju parsed tree for requirement 3.2.5            | 91   |

| B.14 | Enju parsed tree for requirement 3.2.7            | 92   |

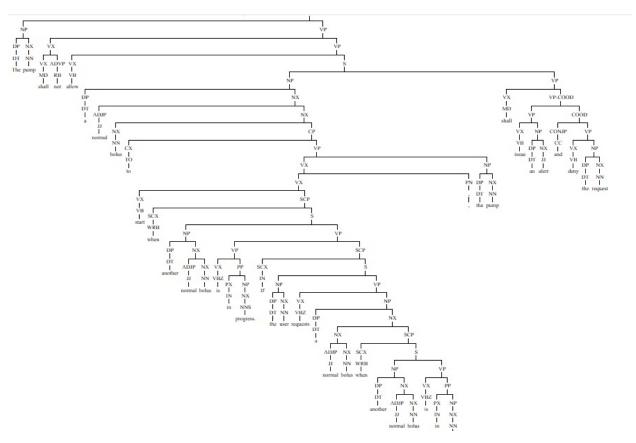

| B.15 | Enju parsed tree for requirement 1.2.8            | 93   |

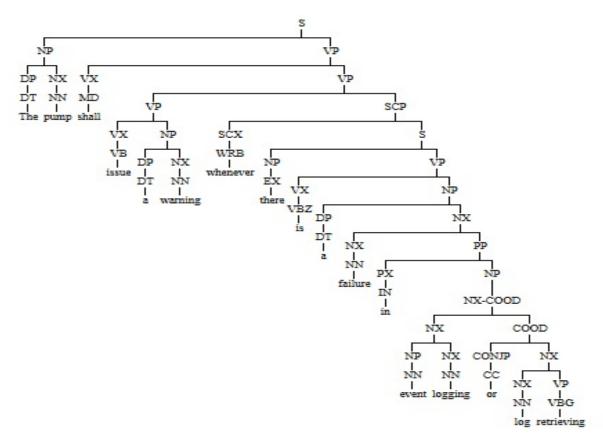

| B.16 | Enju parsed tree for requirement 1.6.1            | 94   |

| B.17 | Enju parsed tree for requirement 1.8.4            | 95   |

| B.18 | Enju parsed tree for requirement 2.2.1            | 96   |

#### 1. INTRODUCTION

#### 1.1. Overview

Safety critical device is a device that its failure can cause a big problem such as loose of money in commercial fields, human health issues or even a death. For example, a medical device that affects patient's life is called a safety critical device. A medical device is an instrument or machine that is used to address, monitor, or control a health situation. It is used for delivering controlled doses of fluid medications to patients such as infusion pump, controlling some important functionalities like pacemaker that helps in controlling patient's heartbeat, or even as simple as monitoring the vital signs such as a blood pressure monitor. Medical devices like infusion pumps, pacemaker, etc. must be safe which means that failure is unacceptable. Software development cycles usually have testing processes to explore expected issues, however, it is not considered to be a comprehensive technique, it can catch errors but can not prove their absence. A proof of system correctness becomes essential, this proof can be accomplished by the use of verification processes such as formal verification, our work presents formal verification processes addressing safety issues in the safety critical devices.

#### 1.2. Motivation

Ensuring the correctness of control software used in safety-critical devices is still an ongoing challenge [1]. For example, from 2001 to 2017, the Food and Drug Administration (FDA) has issued 54 Class-1 recalls on infusion pumps (medical devices used to deliver controlled doses of fluid medications to patients intravenously) due to software issues [2]. Class-1 recalls are applied to medical device models whose use can cause serious adverse health consequences or death. With the advent of Internet of Things (IoT), such safety-critical embedded devices incorporate a whole slew of additional functionality to interface with the network and other components, in addition to their core control functions. These additional functions significantly exacerbate the challenge of ensuring that the core functionality of the control software is correct and intact. Critical devices such as insulin pump still have safeness issues which need valuable software amendments to assure the reliability on design level, this can be handled by either appending new safety insurance functionalities to fix existing hazards, or modifying some defined functionalities that cause faulty behaviours. Since

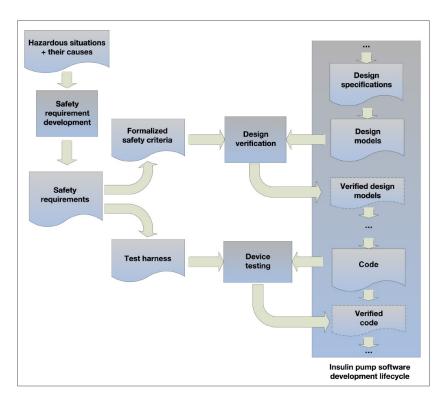

critical devices are considered as real time systems, most of their functionalities have well defined timing conditions must be met else wise the system will fail. System functionalities keeping the system safe are called safety requirements, they are usually written in natural language, therefor, embedding them into the design is a difficult job, requirements need to be transformed into formal presentation (specifications). A procedure to address the gap between informal and formal requirements is required, this is the first goal of this thesis, we propose a structured method to transform requirements in natural language into formal presentation. Embedding the safety requirements in a formal form is not enough to assure the system correctness, critical systems should be checked before use especially medical devices. Testing is the commonly used process to check the software, but it is not sufficient because it does not check all system's functionalities comprehensively, it can only help in finding some errors but not all of them, it should be complemented or even replaced by other techniques such as formal methods [3]. Formal verification can provide proofs of correctness of the system such as model checking, static analysis, and program proof. In our work, we utilize model checking in verifying the transformation procedure of a case study requirements to make sure that formal presentation meets safety requirements. In addition, we study refinement based verification which is a scalable verification technique, actually it is not commonly used because: 1) It requires formal specifications in transition system forms. 2) It requires to build functions called refinement maps which is a complex and difficult mission. We present solutions to address both obstacles by proposing algorithms for each job. Our proposed algorithms are successfully applied on safety requirements for infusion pumps proposed by group of researcher with the help of the FDA [4] [5] as a case study. The existence of safety requirements for infusion pump is considered a motivation of us, the new proposed safety requirements are based on a comprehensive knowledge of the common existing hazards. Figure 1.1 illustrates the process of integrating safety requirements into software development life-cycle, this model needs to be implemented, here our engineering model takes place.

#### 1.3. Problem Statement

#### 1.3.1. Testing

Testing is a process evaluates if the software meets the desired requirements. Despite the fact that testing is the dominant verification technique currently used in commercial design cycles [6], testing can only show the presence of faults, but it never proves their absence [7]. Although it

Figure 1.1. Integrating safety requirements into software development life cycle [4].

checks the system functionalities, this process is time consuming because each function should be tested individually. Large systems might have millions of functions, this makes testing insufficient. Alternate verification processes should be applied to the software design in conjunction with testing to assure system correctness and reliability. Formal verification can address testing limitations by providing proofs of correctness for software safety. Intel [8], Microsoft [9] and [10], and Airbus [11] have successfully applied formal verification processes.

#### 1.3.2. Formal Verification

Formal verification is a proofing process of the correctness of system properties, it shows if the system is acting as specified by its requirements or not [12]. it is considered as the only way guarantees that the system is free from errors [13]. This verification method uses the system mathematical model to assure its correctability [12]. In this thesis, we study two verification process; model checking and refinement based verification as explained below.

#### 1.3.2.1. Model Checking

To reduce the reliance on testing, model checking technique is used to check the correctness of software designs. This verification system can be applied early on a design cycle, or even late on the final design [14]. A model checker is a tool that can check if a model satisfies a set of properties. The properties have to be expressed in a temporal logic. NuSMV is a well structured, flexible, robust, open and documented tool for model checking [15]. NUSMV allows for the representation of synchronous and asynchronous finite state systems, in additional to analyzing of specifications expressed in Computation Tree Logic (CTL) and Linear Temporal Logic (LTL) [16]. In our work, we perform evaluations of transition systems using the NuSMV model checker. Another model checker called UUPPAL is specifically designed for verifying real-time systems. It is based on the timed automata theory [17]. Our work uses UUPPAL to verify resulting transition systems with timing constraints.

#### 1.3.2.2. Refinement Based Verification

Refinement-based verification [18] is a formal verification technology that has been demonstrated to be applicable to the verification of embedded control software at the object-code level [19]. In formal verification and refinement-based verification, typically the design artifact to be verified is called the implementation and the specification is a formal model that captures the correct functionality of the implementation. The goal of refinement-based verification is to mathematically prove that the implementation behaves correctly as defined by the specification. In refinementbased verification, both the implementation and specification are modeled as transition systems and timed transition systems if timing specifications are existed. Our verification process is based on the theory of Well-Founded Equivalence Bisimulation refinement. A detailed description of this theory can be found in [18]. Here, we give a very high-level overview of the key concepts. As stated earlier, WEB refinement provides a notion of correctness that can be used to check an implementation TS against a specification TS. One of the key features is that WEB refinement accounts for stuttering, which is the phenomenon where multiple but finite transitions of the implementation can match a single transition of the specification. This is a very key feature because the control code implements many functions and only some of these functions may be relevant to the safety property being verified. Therefore, the code may be doing a number of things that do not relate to the property and will therefore be stuttering a lot w.r.t. the specification. Another key feature of WEB refinement is refinement maps, which is the focus of this work. Refinement maps are functions that map implementation states to specification states. There is a lot of flexibility in how

Requirement 1.1.1: The pump shall suspend all active basal delivery and stop any active bolus during a pump prime or refill. It shall prohibit any insulin administration during the priming process and resume the suspended basal delivery, either a basal profile or a temporary basal, after the prime or refill is successfully completed. [4]

(a) Safety requirement 1.1.1 in natural language.

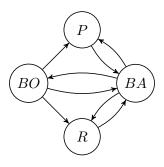

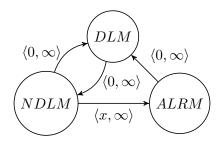

(b) Formal specification representation of requirement 1.1.1.

Figure 1.2. Requirement 1.1.1 in both natural language and formal forms.

refinement maps can be defined. This allows for low-level implementations to be verified against high-level specifications.

**Definition 1** (WEB Refinement): Let  $M = \langle S, R, L \rangle$ ,  $M' = \langle S', R', L' \rangle$ , and  $r: S \to S'$ . M is a WEB refinement of M' with respect to refinement map r, written  $M \approx r$  M', if there exists a relation, B, such that  $\langle \forall s \in S :: sB(r.s) \rangle$  and B is a WEB on the  $TS \langle S \uplus S', R \uplus R', L \rangle$ , where L.s = L'(s) for s and S' state and L.s = L'(r.s) otherwise.

Sections 1.3.2.3 and 1.3.2.4 explains the main obstacles of applying refinement based verification.

#### 1.3.2.3. Formal Specifications

Formal specification is a mathematical presentation of system requirements. One of the crucial challenges in applying refinement-based verification to commercial devices is the availability of formal specifications. For commercial devices, typically, the specification of a device is given as natural language requirements. There are many approaches towards transforming natural language requirements to formal specifications, however none targeted towards refinement-based verification. This work presents a novel methodology to transform natural language requirements into formal specifications to be used in the context of refinement based verification. The new methodology is applied on insulin pump safety requirements which were proposed to solve the common hazards of insulin pump models in the market. Figure 1.2 shows an example of an insulin pump safety requirement (Requirement 1.1.1). Figure 1.2a shows the requirement in natural language, while Figure 1.2b shows the resulting formal specification after applying our methodology.

#### 1.3.2.4. Refinement Maps

One of the key features of refinement-based verification is the use of refinement maps, which are functions that map implementation states to specification states. In practice, these refinement maps have a very favorable property in that they abstract out behaviors of the implementation not relevant to the specification, but only after determining that these additional behaviors do not actually impact the behaviors of the implementation relevant to the specification. This property of refinement maps makes the refinement-based verification very suitable for the verification of control software used in IoT devices as refinement maps can be used to abstract out the additional functionality of software in IoT devices; again, only after determining that these additional functionality are not impacting the behavior of the core functionality of the implementation as defined by the specification. Historically, one of the reasons that refinement-based verification is much less explored than other formal verification paradigms such as model checking is that the construction of refinement maps often requires deep understanding and intuitions about the specification and implementation [20]. However, once a refinement map is constructed, the benefit is that refinementbased verification is a very scalable approach for dealing with low-level artifacts such as real-time object code verification. We build refinement maps corresponding to formal specifications related to infusion pump safety and we also propose three possible generic refinement map templates, which is the first step toward automating the construction of refinement maps. Recently, we present a synthesising procedure of refinement maps, This is an automation procedure to choose a refinement map template based on heuristic data. This methodology is applied on safety requirements of insulin pump based on heuristics that are developed based on the output of the Enju parser to select a refinement map template for each atomic proposition.

#### 1.4. Thesis Outline

The remainder of the thesis consists of the following chapters:

• Chapter 2 presents a novel approach that can synthesize natural language requirements to formal specifications that are useful for refinement-based verification. The proposed approach addresses both functional and timing requirements and has been demonstrated in the context of safety requirements for software control of infusion pumps. The ability to model and validate the system properties for critical systems at the requirements level supports the

detection of design errors during the early stages of a software development life cycle and helps reduce the cost of later redesign activities.

- In Chapter 3, we develop refinement maps for various safety properties concerning the soft-ware control operation of insulin pumps. We also identify possible generic templates for construction of refinement maps as a first step towards developing a process to construct refinement maps in an automated fashion. Finally, we develop a synthesising procedure of refinement maps. Heuristics are developed based on the output of the Enju parser to select a refinement map template for each atomic proposition.

- In Chapter 4, we summarize the problems and how our work presents solutions for each issue.

In addition, some suggested future directions are presented.

- Chapter 5 states the safety requirements we work on, they are written as in the main source.

- Chapter 6 is an appendix of parsed trees for all used safety requirements using an English parser called Enju.

Note that our work studied the correctness of critical systems, transforming natural language requirements into formal specifications will help the designers to include safety requirements easily to assure that the studied system is working correctly as specified. however, our work does not address the reliability issues but it can help indirectly in adding safety requirements that are proposed specially to solve reliability bugs.

#### 1.5. References

- [1] Eman M Al-qtiemat, Sudarshan K Srinivasan, Mohana Asha Latha Dubasi, and Sana Shuja.

"A Methodology for Synthesizing Formal Specification Models From Requirements for Refinement based Object Code Verification". In: The Third International Conference on Cyber Technologies and Cyber Systems. IARIA. 2018, pp. 94–101.

- [2] FDA. List of Device Recalls, U.S. Food and Drug Administration (FDA). last accessed: 2018-09-10. 2018. URL: https://www.accessdata.fda.gov/scripts/cdrh/cfdocs/cfRES/res.cfm.

- [3] Xavier Leroy. "Formal verification of a realistic compiler". In: Communications of the ACM 52.7 (2009), pp. 107–115.

- [4] Yi Zhang, Raoul Jetley, Paul L Jones, and Arnab Ray. "Generic safety requirements for developing safe insulin pump software". In: Journal of diabetes science and technology 5.6 (2011), pp. 1403–1419.

- [5] Yi Zhang, Paul L Jones, and Raoul Jetley. "A hazard analysis for a generic insulin infusion pump". In: *Journal of diabetes science and technology* 4.2 (2010), pp. 263–283.

- [6] SMK Quadri and Sheikh Umar Farooq. "Software Testing-Goals, Principles, and Limitations". In: *International Journal of Computer Applications* 6.9 (2010), pp. 7–10.

- [7] Edward Miller and William E Howden. Tutorial, software testing & validation techniques.

IEEE Computer Society Press, 1981.

- [8] R. Kaivola et al. "Replacing Testing with Formal Verification in Intel CoreTM i7 Processor Execution Engine Validation". In: Computer Aided Verification, 21st International Conference, CAV, Grenoble, France, June 26 July 2, 2009. Proceedings. Ed. by Ahmed Bouajjani and Oded Maler. Vol. 5643. Lecture Notes in Computer Science. Springer, 2009, pp. 414–429. ISBN: 978-3-642-02657-7. DOI: 10.1007/978-3-642-02658-4\\_32. URL: https://doi.org/10.1007/978-3-642-02658-4%5C\_32.

- [9] Thomas Ball, Byron Cook, Vladimir Levin, and Sriram K. Rajamani. "SLAM and Static Driver Verifier: Technology Transfer of Formal Methods inside Microsoft". In: *Integrated Formal Methods, 4th International Conference, IFM, Canterbury, UK, April 4-7, 2004, Proceedings.* Ed. by Eerke A. Boiten, John Derrick, and Graeme Smith. Vol. 2999. Lecture Notes in Computer Science. Springer, 2004, pp. 1–20. ISBN: 3-540-21377-5. DOI: 10.1007/978-3-540-24756-2\\_1. URL: https://doi.org/10.1007/978-3-540-24756-2\Sc\_1.

- [10] Karthikeyan Bhargavan et al. "Formal verification of smart contracts: Short paper". In: Proceedings of the 2016 ACM Workshop on Programming Languages and Analysis for Security. ACM. 2016, pp. 91–96.

- [11] D. Delmas et al. "Towards an industrial use of FLUCTUAT on safety-critical avionics software". In: International Workshop on Formal Methods for Industrial Critical Systems. Springer. 2009, pp. 53–69.

- [12] Robert M Keller. "Formal verification of parallel programs". In: Communications of the ACM 19.7 (1976), pp. 371–384.

- [13] Gerwin Klein et al. "seL4: Formal verification of an OS kernel". In: *Proceedings of the ACM SIGOPS 22nd symposium on Operating systems principles.* 2009, pp. 207–220.

- [14] Gerard J Holzmann. The SPIN model checker: Primer and reference manual. Vol. 1003.

Addison-Wesley Reading, 2004.

- [15] Alessandro Cimatti, Edmund Clarke, Fausto Giunchiglia, and Marco Roveri. "NuSMV: a new symbolic model checker". In: *International Journal on Software Tools for Technology Transfer* 2.4 (2000), pp. 410–425.

- [16] Roberto Cavada et al. "Nusmv 2.4 user manual". In: CMU and ITC-irst (2005).

- [17] Gerd Behrmann, Alexandre David, and Kim G Larsen. "A tutorial on uppaal". In: Formal methods for the design of real-time systems. Springer. 2004, pp. 200–236.

- [18] Panagiotis Manolios. "Mechanical Verification of Reactive Systems". last accessed: 2018-10-10. PhD thesis. University of Texas at Austin, Aug. 2001. URL: http://www.ccs.neu.edu/home/pete/research/phd-dissertation.html.

- [19] Mohana Asha Latha Dubasi, Sudarshan K Srinivasan, and Vidura Wijayasekara. "Timed refinement for verification of real-time object code programs". In: Working Conference on Verified Software: Theories, Tools, and Experiments. Springer. 2014, pp. 252–269.

- [20] Martién Abadi and Leslie Lamport. "The existence of refinement mappings". In: *Theoretical Computer Science* 82.2 (1991), pp. 253–284.

# 2. SYNTHESIS OF FORMAL SPECIFICATIONS FROM REQUIREMENTS FOR REFINEMENT BASED REAL TIME OBJECT CODE VERIFICATION

#### 2.1. Introduction

Ensuring the correctness of control software used in safety-critical embedded devices is still an ongoing challenge [1]. For example, from 2001 to 2017, the Food and Drug Administration (FDA) has issued 54 Class-1 recalls on infusion pumps (medical devices used to deliver controlled doses of fluid medications to patients intravenously) due to software issues [2]. Class-1 recalls are applied to medical device models whose use can cause serious adverse health consequences or death. With the advent of IoT, such safety-critical embedded devices incorporate a whole slew of additional functionality to interface with the network and other components, in addition to their core control functions. These additional functions significantly exacerbate the challenge of ensuring that the core functionality of the control software is correct and intact.

Safety critical devices such as insulin pump still have safety issues which need valuable software amendments to assure the reliability on design level, this can be handled by either appending new safety insurance specifications to fix existing hazards, or modifying some defined specifications that cause faulty behaviours. Since safety critical devices are considered as real time systems, most of their specifications have well defined timing constraints must be met else wise the system will fail. This chapter works with both functional and timing specifications (called functional and timing requirements), they are basically written in natural language and need to be transformed into a formal model, then it can be tested using a formal verification method. The use of formal verification has become an industry standard when addressing software correctness of safety-critical

The content of this chapter has been published in the International Journal on Advances in Internet Technology 2019. The material in this chapter was co-authored by Eman M. Al-Qtiemat, Sudarshan Srinivasan, Zeyad Al-Odat, Mohana Asha Latha Dubas, and Sana Shuja. Eman M. Al-Qtiemat had primary responsibility for conducting experiments and collecting results. Eman M. Al-Qtiemat was the primary developer of the conclusions that are advanced here. Eman M. Al-Qtiemat also drafted and revised all versions of this chapter. Sudarshan Srinivasan and Mohana Asha Latha Dubas drafted and revised all versions of this chapter. Sudarshan Srinivasan served as proofreader.

devices. There are many success stories and commercial adoption of formal verification processes. Examples include Intel [3], Microsoft [4] and [5], and Airbus [6].

Refinement-based verification [7] is a formal verification technology that has been demonstrated to be applicable to the verification of embedded control software at the object-code level [8]. In formal verification and refinement-based verification, typically the design artifact to be verified is called the implementation and the specification is a formal model that captures the correct functionality of the implementation. The goal of refinement-based verification is to mathematically prove that the implementation behaves correctly as defined by the specification. In refinement-based verification, both the implementation and specification are modeled as transition systems and timed transition systems if timing specifications are existed.

One of the key features of refinement-based is the use of refinement maps, which are functions that map implementation states to specification states. In practice, these refinement maps have a very favorable property in that they abstract out behaviors of the implementation not relevant to the specification, but only after determining that these additional behaviors do not actually impact the behaviors of the implementation relevant to the specification. This property of refinement maps makes the refinement-based verification very suitable for the verification of control software used in Internet of Things (IoT) devices as refinement maps can be used to abstract out the additional functionality of software in IoT devices; again, only after determining that these additional functionality are not impacting the behavior of the core functionality of the implementation as defined by the specification.

One of the crucial challenges in applying refinement-based verification to commercial devices is the availability of formal specifications. For commercial devices, typically, the specification of a device is given as natural language requirements. There are many approaches towards transforming natural language requirements to formal specifications, however none targeted towards refinement-based verification. In this chapter, we present methodologies for transforming natural language requirements (both functional and timing) into formal specifications that can be used in the context of refinement-based verification.

The rest of the chapter is organized as follows. An overview of the background is presented in Section 2.2. Section 2.3 details the related work. A formal model describing the synthesis procedure of functional requirements is presented in Section 2.4, while Section 2.5 presents a different formal

model describing the synthesis procedure of timing requirements. Section 2.6 details the case study. Section 2.7 gives the verification results for the proposed formal model. Conclusions and direction for future work are noted in Section 2.8.

#### 2.2. Background

This section explores the parsing tree, the definition of transition systems and the definition of timed transition systems as key terms related to our work.

#### 2.2.1. Parsing Tree

A parse tree is an ordered tree that pictorially represents how words in a sentence are connected to each other. The connection between each word in the sentence gives the syntactic categories for the sentence. The parsing process represents the syntactic analysis of a sentence in natural language. For example, when the parsing process is applied on a simple sentence like "Adam eats banana", the parse tree categorizes the two parts of speech: N for nouns (Adam, banana) and V for the verb (eats). Here N, V are the syntactic categories. The parsing process is considered to be a preprocessing step for some applications, where natural language should be converted into other forms. Usually, the system requirements are written in natural language, which needs to be converted into a structural form that can then be used to create the transition system(s) (explained in Section 2.2.2). Enju [9] is an English consistency-based parser, which can process very long complex sentences like system requirements using an accurate analysis (the accuracy relation is around 90 percent of news articles and bio-medical papers). Besides, Enju is a high-speed parser with less than 500 msec per sentence. The output is the resulting tree in an XML format which is considered to be one of the commonly used formats by various applications. As will be described later, the case study used to describe the proposed methodology is from the bio-medical area, Enju was the perfect tool as the natural language processing (NLP) parser.

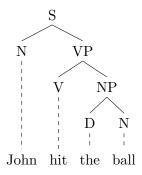

Figure 2.1 shows a simple tree example using Enju. Here, Enju distinguishes between terminal nodes (John is a terminal node) and non-terminal nodes (VP is a verb phrase). The abbreviations of the syntactic categories of Figure 2.1 are: S stands for sentence (the head of the tree), N stands for noun, VP stands for verb phrase (which is a subtree), NP stands for noun phrase, V stands for verb, and finally D stands for determiner (comes with noun phrases). Using these syntactic categories, we have developed an extraction technique that would help in translating the natural language to a formal model of the requirements.

Figure 2.1. A simple example of a parsing tree using Enju parser[10].

#### 2.2.2. Transition Systems

The implementation and specification in refinement-based verification are represented using Transition Systems (TSs) [7, 8]. The definition of a TS is given below:

**Definition 2** A TS  $M = \langle S, R, L \rangle$  is a three tuple in which S denotes the set of states,  $R \subseteq SXS$  is the transition relation that provides the transition between states, and L is a labeling function that describes what is visible at each state.

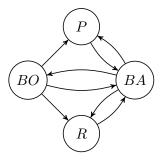

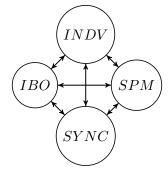

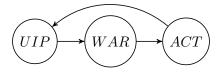

Figure 2.2. An example of a transition system (TS).

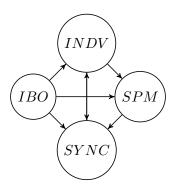

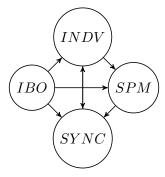

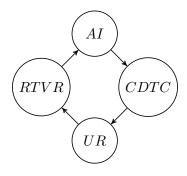

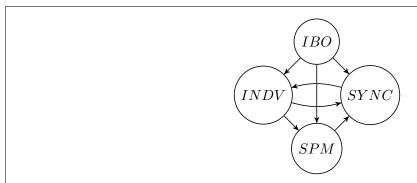

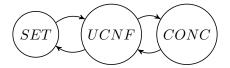

An Atomic Proposition (AP) is a statement that can be evaluated to be either true or false. The labeling function maps state to the APs that are true in every state. An example of a TS is shown in Figure 2.2. Here  $S = \{\text{IBO, SPM, SYNC, INDV}\}$ ,  $R = \{(\text{IBO, SPM}), (\text{SPM, SYNC}), (\text{SYNC, INDV}), (\text{INDV, SYNC}), (\text{INDV, SPM}), (\text{IBO, INDV})\}$  and, L(SPM) represents the atomic propositions that are true for the SPM state. Similarly, labeling function can be applied to all the states in this TS.

#### 2.2.3. Timed Transition Systems

Some applications have requirements with timing conditions on the state's transitions called as timing requirements. Timing requirements explain the system behaviour under some timing constraints. Timing constraints are very important especially if we deal with a critical real time systems. As mentioned in the previous section (Sec 2.2.2), transition systems are used to represent the implementation and specification in refinement-based verification, however they do not contain timing requirements. Hence, in the verification of real time systems that contain timing constraints, timed transition systems (TTSs) [8] are used to represent the implementation and specification.

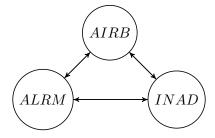

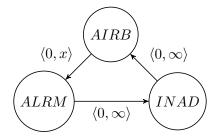

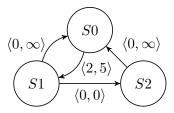

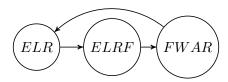

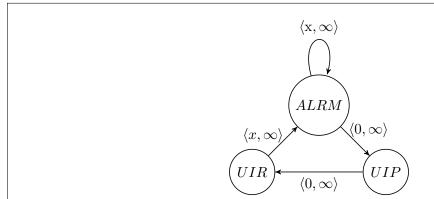

Figure 2.3. An example of a timed transition system (TTS)

**Definition 3** A TTS  $M_t = \langle S, R_t, L \rangle$  is a three tuple in which S denotes the set of states and L is a labeling function that describes what is visible at each state. The state transition  $R_t$  has the form of  $\langle x, y, l_t, u_t \rangle$  where  $x, y \in S$  and  $l_t, u_t \in N$  represents the lower and upper bounds as the timing condition for the transition.

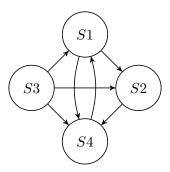

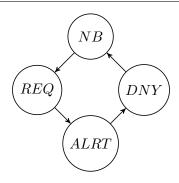

Figure 2.3 shows an example of a timed transition system that consists of three states  $\{S1, S2, S3\}$ , for instance; if the system is in state S1 it can go to state S2 only between 1 and 4 units of time, while going from S2 to S3 the time is zero meaning that it should happen immediately, and so on.

#### 2.3. Related Work

In the last few years, there has been a tremendous growth in finding the optimal technique of requirement transformation into a formal model. While most of them proposed system-driven models, our approach is user-driven to ensure a safe product.

Automatic Requirements Specification Extraction from Natural Language (ARSENAL) [11] is a system based framework that applies some semantic parsers in multi-level to get the grammatical

relations between words in the requirement. ARSENAL transforms natural language requirements into formal and logical forms expressed in Symbolic Analysis Laboratory (SAL) (a formal language to describe concurrent systems), and Linear Temporal Logic (LTL) (a mathematical language that describes linear time properties) respectively. The LTL formulas are then used to build the SAL model. Multiple validation checks are applied on Natural Language Processing (NLP) stage and LTL formulas to check for their correctness. However, ARSENAL records some inaccuracies in NLP stage that need a user intervention.

Aceituna et al. [12] have proposed a front end framework that builds a model to exhibit the system behavior (for synchronous systems only) and help in creating temporal logic properties automatically. This framework can be used before applying the model checking technique, it exposes accidental scenarios in the requirements. The framework is designed in a manner that helps in understanding the errors in a non-technical manner for users who do not have a formal background. In contrast, our work does not need the temporal logic in defining the specifications for a model.

A semantic parser has been developed by Harris [13] to extract a formal behavioral description from natural language specifications. The proposed semantic parser was employed to extract key information describing bus transactions. The natural language descriptions are then converted to verilog (a hardware description language) tasks.

Kress-Gazit et al. [14] have proposed a human-robot interface to translate natural language specification into motions. This interface allows a user to instruct the robot using a controller. LTL formulas are employed to formalize the desired behavior requested by the user.

An approach supporting property elucidation (called PROPEL) has been introduced by Smith et al. [15], it provides templates that capture properties for creating property pattern. Natural language and finite state automation are used to represent the templates.

Two approaches have been proposed by Shimizu [16] to solve the ambiguity of natural language specifications using formal specification. The first approach simplifies the formal specification development for the popular PCI bus protocol and the Intel Itanium bus protocol. The second approach explains how formal specifications can help in automating many processes that are now done manually.

A natural language parsing technique has been used with the default reasoning, which is a requirement formalism to support requirement development, this work helps stakeholders to easily deal with requirements in a formal manner, in addition, a method has been proposed for discovering any existed requirement's inconsistencies. A prototype tool called CARL was used for implementation and verification by Zowghi et al. [17].

Gervasi et al. [18] have also worked on solving the requirement's inconsistencies issues by using a well-known formalism called monotonic logic, it has been used especially for requirement's transformation. Multiple natural language processing tools [19–22] in additional to grammatical analysis methodologies for requirement's development have been done to get requirements in a formal manner.

Bouyer et al. [23] have recently presented a survey on timed automata and how it can be applied for model checking of real-time systems. This survey has summarized the work that has been done since the inception of timed automata in the early 1990s till now. The timing information in real-time models is expressed as temporal logic. However, the survey does not specify gathering timing information from natural language requirements, which has been the focus of our work.

Knorreck et al. [24] have presented a graphical tool called AVATAR-TEPE (Automated Verification of reAl Time softwARe - TEmporal Property Expression Language), in which the logical and temporal properties are expressed in formal language. This tool can perform all tasks from requirement capture to verification in one language and in one environment. However, the tool requires the knowledge of logical and temporal properties to verify the application. The tool is heavily based on property modeling.

A standardized testing method for distributed real-time cyber-physical systems (CPS) has been proposed by Shrivastava et al. [25]. Temporal properties have been used to express the timing constraints. Peters et al. [26] have proposed a new language that considers timing requirement and checks for errors in the description of the timing constraints. Kang et al. [27] have presented a model-driven approach to verify the timing requirements for automotive systems at the design level. However, in all these works, gathering the timing constraints from natural language requirements, which has been the focus of this paper, has not been addressed.

Carvalho et al. [28] have proposed a symbolic model for translating natural language requirements to a formal model which consider time. Model-based testing techniques are then applied

to these formal models. Hassine [29] has presented a formal framework to describe, simulate and analyze real-time systems. This framework considers timing requirements. However, this proposed framework is yet to be applied on large scale industrial projects. In these works, even though the timing requirements are considered, none of the these works are targeted at refinement based verification.

The main advantages of our work over prior algorithms in requirements engineering is its ability to generate a full formal model directly from natural language requirements by an expert supervision to emphasis on the safety transformation. Also, our work does not require that the expert user know any temporal logic languages which has been case for most of the current literature.

#### 2.4. Formal Model Synthesis Procedure for Functional Requirements

The first step of computing the TSs is to extract the APs from the requirements. We have developed three Atomic Proposition Extraction Rules (APERs) that work on the parse tree of the requirement obtained from Enju. The resulting APs are then used to compute the states and transitions. The APERs are described next.

#### 2.4.1. Atomic Proposition Extraction Rule 1 (APER 1)

APER 1 is based on the hypothesis that noun phrases in a requirement correspond to APs. Each subtree of the parse tree with an NX root (called an NX head) corresponds to a noun phrase and hence an AP. Therefore, APER 1 computes the subtrees corresponding to NX heads. If NX heads are nested, then the highest-level NX head is used to compute the AP. The terminal nodes of the subtree are conjoined together to form the noun phrase. APER 1 returns AP-list, which is the set of APs corresponding to a parse tree.

#### Procedure 1 APER1

```

Require: Parse-tree

1: AP-list \leftarrow \emptyset;

2: for each n \in \text{TerminalNodes}(\text{Parse-tree}) do

Start-cat = head(head(n));

3:

if Start-cat = NX then

4:

X = \text{Sub-tree(Start-cat)};

5:

while (\text{head}(X) = \text{NX}) \vee (\text{head}(X) = \text{COOD})

6:

\vee (head(X) =NX-COOD) do

X = \text{Sub-tree}(\text{head}(X));

7:

8:

AP-list \leftarrow AP-list \cup TerminalNodes(X);

```

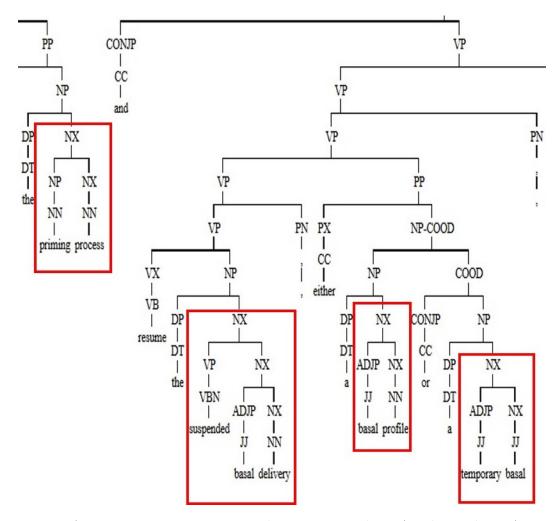

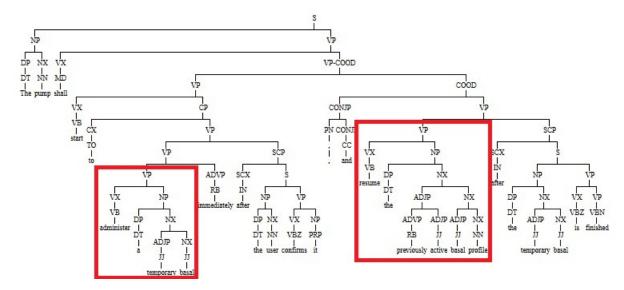

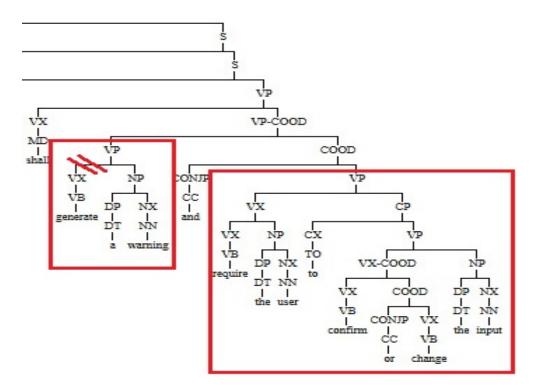

Figure 2.4. An Enju parsing tree portion shows some resulting APs by applying APER 1.

We now describe the procedure corresponding to APER 1 in detail. Firstly, AP-List is initialized to the empty set (line 1). The procedure then iterates through each terminal node n (line 2). The head of a node is its parent. If a terminal node is part of an NX subtree, its level two head will be marked as NX, which is checked in line 3. The level-two NX node of the terminal node is stored in variable State-cat. If the Start-cat is of NX category (line 4), a function called Sub-tree is used to get the resulting subtree (line 5), which is stored in variable X. A while loop is used to traverse the tree of X upwards checking if the head syntactic category is NX or COOD or NX-COOD (line 6). Only when one of the conditions is satisfied the subtree is stored in X (line 7). The terminal nodes of the resulting sub tree 'X' will be added to AP-List as a new suggested AP (line 8). Figure 2.4 gives a sub tree example for APER 1.

Note that APER 1 may result in the same AP being duplicated. Duplicates are checked and removed from the AP list in the overall approach.

Figure 2.5. An Enju parsing tree portion of requirement 2.2.2 shows some resulting APs by applying APER 1.

As shown in Figure 2.4, the terminal nodes 'the' and 'priming' does not have head(head(n)) = NX. The first terminal node that has the NX category is 'process'. Traversing upwards, the NX related categories gives us the subtree which contains 'priming process'. This now constitutes the first AP for this part of requirement. Applying the APER 1 rule on the visible part of the sentence in Figure 2.4 gives us the following APs: 'priming process', 'suspended basal profile', 'basal profile', and 'temporary basal'. Also, Figure 2.6 and Figure 2.5 show some resulting APs by applying APER 1 on requirement 1.8.2 and 2.2.2 respectively from [30].

#### 2.4.2. Atomic Proposition Extraction Rule 2 (APER 2)

APER 2 and APER 3 correspond to the two other parse tree patterns that also lead to noun phrases. APER 2 examines the parse tree for noun categories along with its upper verb head. APs will be the conjoined terminal nodes of the resulting sub tree. APER 2 states that APs are the terminal nodes under the head VP passing through NX (or its related phrases such as NX-COOD, COOD), NP (or its related phrases NP-COOD, COOD), and VX phrase.

APER 2 is built on top of APER 1 to get atomic propositions for requirements that APER 1 is not able to collect. While APER 1 looks only for APs that are noun phrases, APER 2 looks for noun phrases that are further characterized by verb phrases. For example, if APER 1 finds the AP "suspended basal delivery," APER 2 will find "resume the suspended basal delivery."

Figure 2.6. An Enju parsing tree portion of requirement 1.8.2 shows some resulting APs by applying APER 1.

#### Procedure 2 APER 2

```

Require: Parse-tree

1: AP-list \leftarrow \emptyset;

2: for each n \in \text{TerminalNodes}(\text{Parse-tree}) do

Start-cat = head(head(n));

X_1 \leftarrow \emptyset;

4:

if Start-cat = NX then

5:

X = \text{Sub-tree(Start-cat)};

6:

7:

while (head(X) = NX) \lor (head(X) = COOD)

\vee (head(X) =NX-COOD ) do

X = \text{Sub-tree}(\text{head}(X));

8:

while (\text{head}(X) = \text{NP}) \vee (\text{head}(X) = \text{COOD})

9:

\vee \text{ (head}(X) = \text{NP-COOD)} \text{ do}

X_1 = \text{Sub-tree}(\text{head}(X));

10:

if (\text{head}(X_1) = \text{VX}) \land (\text{head}(\text{head}(X_1)) = \text{VP}) then

11:

X = \text{Sub-tree}(\text{head}(\text{head}(X_1));

12:

else

13:

if (\text{head}(X_1) = \text{VP}) then

14:

X = \text{Sub-tree}(\text{head}(X_1);

15:

AP-list \leftarrow AP-list \cup TerminalNodes(X);

16:

```

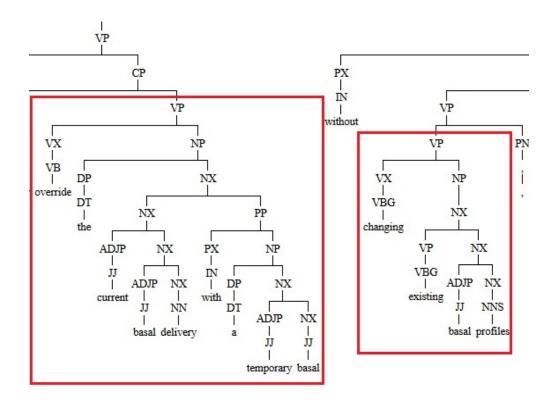

Figure 2.7. An Enju parsing tree portion of requirement 1.2.6 shows some resulting APs by applying APER 2.

APER 1 and APER 2 have the same algorithmic flow until finding the sub tree of X that is the top NX head (line 8). However, APER 2 does not consider the resulting X to be an AP like APER 1 does. Instead, X is the input of the next step. A while loop is used to search if the head category of X is in NP category or one of its related phrases (line 9). Only when the while loop condition is true, the new sub-tree is stored temporarily in the variable  $X_1$  (line 10), where  $X_1$  is a temporary variable initialized to null (line 4). This ensures that X does not change in this step for future use. The search for VX and VP categories is to be performed only when  $X_1$  is not null.

On the successful completion of NP category search, the search for VX category followed by VP categories is performed (line 11). When the if condition is satisfied, X is updated with the new sub-tree (line 12). In the case of failure of the if condition in line 11, a new search for VP category is performed on the head of NP category sub-tree (line 14). On success, X is updated with the new sub-tree (line 15). If either of the if conditions (line 11 and line 14) fail, then X will remain as the sub-tree of NX category. The terminal nodes of the resulting subtree in X is appended to the AP-list (line 16). Figure 2.8 and Figure 2.7 show resulting sub tree examples by applying APER 2.

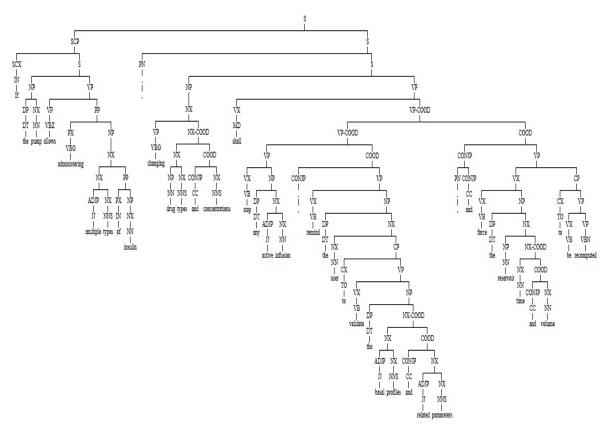

Figure 2.8 shows that the procedure starts from left to right looking for level two NX nodes and traversing upward until higher NX nodes are accounted for. NP phrases are selected to expand the tree. Then choosing the upper level which is VP in this particular case (sometimes its VX  $\rightarrow$  VP). The output of APER 2 for this tree portion is 'override the current basal delivery with a

Figure 2.8. An Enju parsing tree portion shows some resulting APs by applying APER 2.

temporary basal', and 'changing existing basal profiles'. Also, Figure 2.9 shows some resulting APs by applying APER 2 on requirement 1.1.3 from [30].

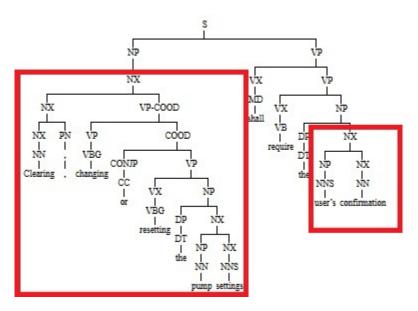

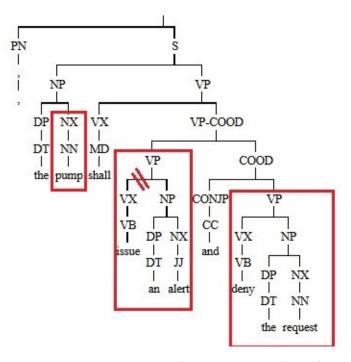

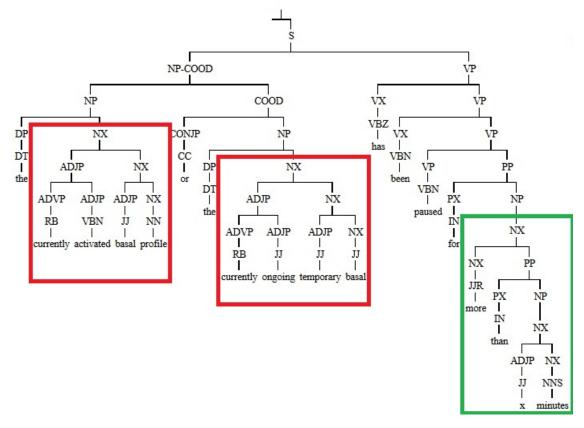

#### 2.4.3. Atomic Proposition Extraction Rule 3 (APER 3)

APER 3 is built on top of APER 2, it explores the verb head levels in the parse tree like APER 2, but APER 3 eliminates some verb phrases that is not part of APs. This elimination is done based on the head of the VP category as illustrated in Procedure 3 below.

APER 3 and APER 2 have the same stream up to line 10. The algorithm starts with initializing temporary variables  $X_1$  and Y to null (line 4). The search for syntactic categories start with the top NX phrase (line 7) and the resultant sub tree is stored in X (line 8). Then, the search begins for the top NP phrase (line 9) and the resultant sub tree is stored in  $X_1$  (line 10) since the sub tree in X is needed for future use. As in APER2, the search for either VX phrase followed by VP phrase or just VP phrase is performed on  $X_1$  and the resultant sub tree is stored in Y (lines 11-15). If and only if Y is not empty then the check on the head syntactic category is performed to ensure that it does not contain CP or COOD categories. In this case, X gets only the right child (line 16-18) i.e. the left child of Y is pruned. On the other hand, if Y has a CP or COOD head, X

Figure 2.9. An Enju parsing tree portion shows some resulting APs by applying APER 2 on requirement 1.1.3.

value will be updated to be equal to Y (line 20). Finally, terminal nodes of the resulting sub tree X will be saved in the AP-list as a new AP. The pruning process (line 18) is done to remove some action verbs which are not part of an AP.

Like APER2, APER3 also works on verb head categories. However, APER3 has some pruning techniques to remove parts of the sentence that should not be part of an AP. Consider the snippet in Figure 2.10, the sub tree "issue an alert" is subjected to left branch pruning to remove the verb 'issue' since such verbs do not add value in the AP. According to the algorithm, since the head node of VP is COOD, only the terminal nodes of the right child are considered as an AP. Applying APER 3 on the visible part of the requirement in Figure 2.10 gives the following APs: 'pump', 'an alert', and 'deny the request'. Also, Figure 2.11 shows some resulting APs by applying APER 3 on requirement 3.2.5 from [30].

The proposed APERs may be used individually or in combination depending on the system requirement and model functionally. However, no one rule is considered to be the best for all models because of the natural language structure.

#### Procedure 3 APER 3

```

Require: Parse-tree

1: AP-list \leftarrow \emptyset;

2: for each n \in \text{TerminalNodes}(\text{Parse-tree}) do

Start-cat = head(head(n));

4:

X_1 \leftarrow \emptyset, Y \leftarrow \emptyset;

if Start-cat = NX then

5:

X = \text{Sub-tree(Start-cat)};

6:

while (\text{head}(X) = \text{NX}) \vee (\text{head}(X) = \text{COOD})

7:

\vee (head(X) =NX-COOD) do

X = \text{Sub-tree}(\text{head}(X));

8:

while (\text{head}(X) = \text{NP}) \vee (\text{head}(X) = \text{COOD})

9:

\vee (head(X) = NP-COOD) do

X_1 = \text{Sub-tree}(\text{head}(X));

10:

if (\text{head}(X_1) = \text{VX}) \land (\text{head}(\text{head}(X_1)) = \text{VP}) then

11:

Y = \text{Sub-tree}(\text{head}(\text{head}(X_1));

12:

else

13:

if (\text{head}(X_1) = \text{VP}) then

14:

Y = \text{Sub-tree}(\text{head}(X_1);

15:

if (Y \neq \emptyset) then

16:

if head(Y) \neq CP) \land (head(Y) \neq COOD) then

17:

X = \text{Sub-tree}(\text{RightChild}(Y));

18:

else

19:

X = Y;

20:

AP-list \leftarrow AP-list \cup TerminalNodes(X);

21:

```

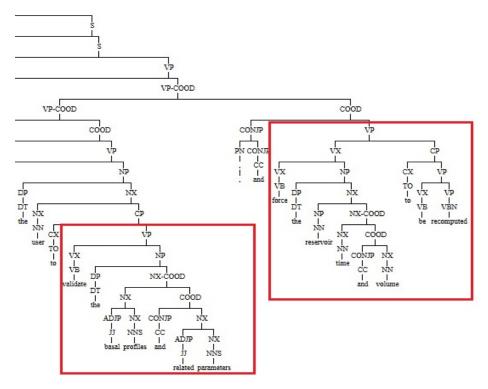

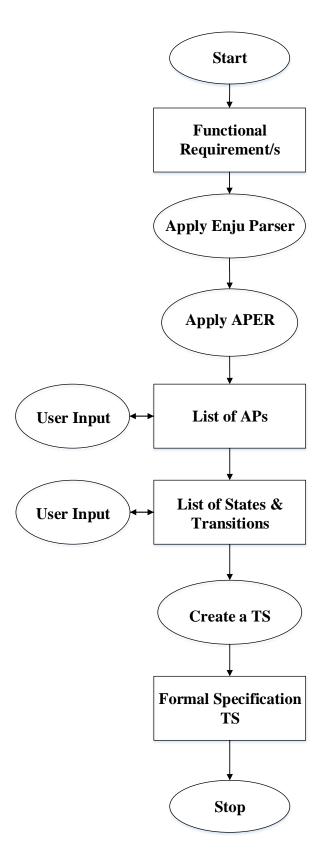

#### 2.4.4. High-Level Procedure for Specification Transition System Synthesis

Procedure 4 shows the overall flow for computing the TSs. A set of system requirements in natural language are fed as input to the procedure. TS-set is the output of the procedure and will contain the set of transition systems that capture the input requirements as a formal model. TS-set is initialized to null (line 1). Each requirement is input to the Enju parser. The parser gives an xml file as output. A function called Get is used to obtain the xml file into the variable Parse-tree (line 3). The xml output in Parse-tree is subjected to the proposed APERs, which give the atomic propositions (APs) as output. APs are stored in the AP-list (line 4). Each requirement is subject to all APERs and the AP-list obtained is the union of the APs produced by each of the rules. The output obtained by using the APERs may contain duplicates, which are eliminated by using the function Eliminate\_Dup (line 5). AP-list is then subjected to an expert user check, where

Figure 2.10. An Enju parsing tree portion shows some resulting APs using APER 3.

the AP(s) might be appended, eliminated or revised based on the expert user's domain knowledge (line 6). Some of the APs maybe expressible as a Boolean function of other APs.

Therefore, next, a truth table (AP-truth-table) is created, where each row corresponds to an AP from AP-list and each column also corresponds to an AP from AP-list (line 7). Each entry in the table is a Boolean value (true or false). Completing the truth table determines the relationship of each AP with the other APs in the AP-list. The truth table is completed by the expert user (line 8). The list of states for the input requirements are stored in the variable S-list. S-list is initialized to null (line 9). oo7 This heuristic has worked well in practice. S-list is subjected to expert user input (line 12).

The transitions of the TS are computed next. The list of transitions (T) is initialized to a transition between every two states using function 'CreateT' (line 13). The transition list is subjected to expert user input (line 14). A transition system (TS) is constructed using the CreateTS function, which takes the transitions (T) and the list of states (S-list) as input (line 15). This transition system (TS) is then added to the transition system set (TS-set) (line 16). The procedure finally returns a set of transition systems for all the requirements in an application (line 17).

Figure 2.11. An Enju parsing tree portion shows some resulting APs by applying APER 3 on requirement 3.2.5.

#### 2.5. Formal Model Synthesis Procedure for Timing Requirements

In this section, the approach is extended to deal with timing requirements. When synthesizing transition systems (TSs), the core activity was the extraction of APs. For synthesizing timed transition system, the core activity is the extraction of APs and TCs. An additional extraction rule is developed, that can be applied on timed requirements not only to get APs but also to extract the timing constraints (TCs) on each state transition.

# 2.5.1. Atomic Proposition and Timing Constrains Extraction Rule (APTCER) for Timed Transition System

This section explains a new proposed rule that analyzes timing requirements to get APs with their corresponding TCs as a base for building TTSs. This rule called Atomic Proposition and Timing Constrains Extraction Rule (APTCER) is specified as Procedure 5 and works as follows. First, the timing requirement is split into smaller phrases that are individually analyzed (lines 1-14 of Procedure 5). These phrases are called Timed Based Sentences (TBSs). Each resulting phrase

# Procedure 4 Procedure for synthesizing TSs from system requirements

```

Require: set of requirements (System-requirements)

1: TS-set \leftarrow \emptyset;

2: for each Reg \in System-requirements do

Parse-tree \leftarrow Get(Req_tree.xml);

AP-list \leftarrow APER(Parse-tree);

4:

5:

AP-list \leftarrow Eliminate_Dup(AP-list);

AP-list \leftarrow USR_IN(AP-List);

6:

7:

AP-truth-table \leftarrow Relation(AP-list);

AP-truth-table \leftarrow USR\_IN(AP-truth-table);

8:

S-list \leftarrow \emptyset;

9:

for each A \in AP-truth-table do

10:

11:

S-list[i] = A_i;

S-list \leftarrow USR_IN(S-list);

12:

T \leftarrow CreateT(S-list);

13:

T \leftarrow USR\_IN(T);

14:

TS \leftarrow CreateTS(T, S-list);

15:

TS-set \leftarrow TS-set UTS;

16:

return TS-set;

17:

```

is then analyzed to extract the APs and TCs in that phrase (lines 15-38 of Procedure 5). The list of APs and TSs are stored in  $\langle AP - list, TC - list \rangle$ .

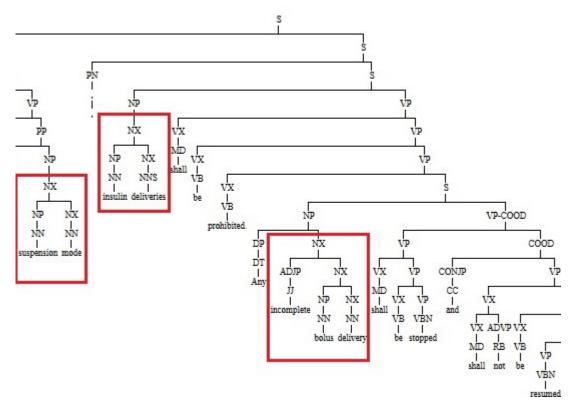

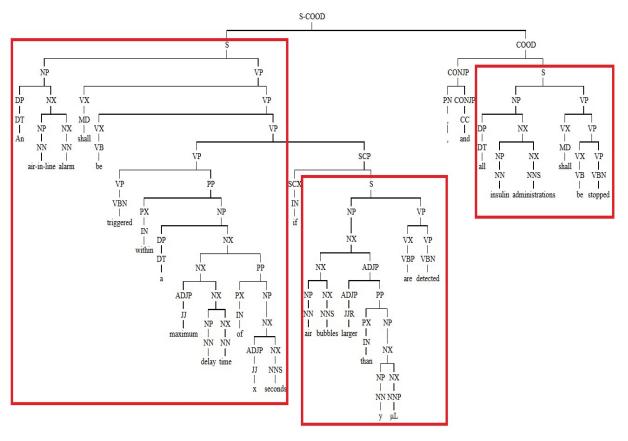

APTCER takes the parse tree of the timing requirement as input. The parse tree is obtained by applying the Enju parser on the timing requirement. APTCER initilizes the list of TBSs (TBS-list) to the empty list (line 1). APTCER then searches for sub-trees with root as "S" and with left child of "NP" and right child as "VP" (lines 2-5). Each such sub-tree is a TBS.

Note that TBSs can be nested in that there can be a TBS inside of a TBS. The nested TBSs need to partitioned and analyzed individually. This is done by searching for sub-trees inside the TBS with "SCP" or "S" roots. Such sub trees are cut out and the resulting TBS is returned (lines 7-13).

Next, the TBSs are analyzed to extract the APs and TCs. The extraction is performed by analyzing both the left child and the right child of the TBS. The left and right sub-trees are assigned to variables A and B, respectively (lines 19 and 23). Then APER 1 is used to analyze both A and B. Through empirical observation, it has been determined that the APs extracted by APER 1 from sub-tree A (line 21, 22) corresponds to APs but the APs extracted by APER 1 from

sub-tree B (line 25, 26) corresponds to TCs. The resulting AP-list and TC-list are corresponds to one TBS (line 27), the TBS's pair is saved in the final TBS-list (line 28).

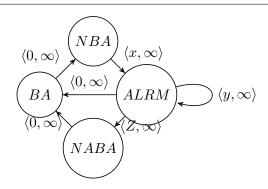

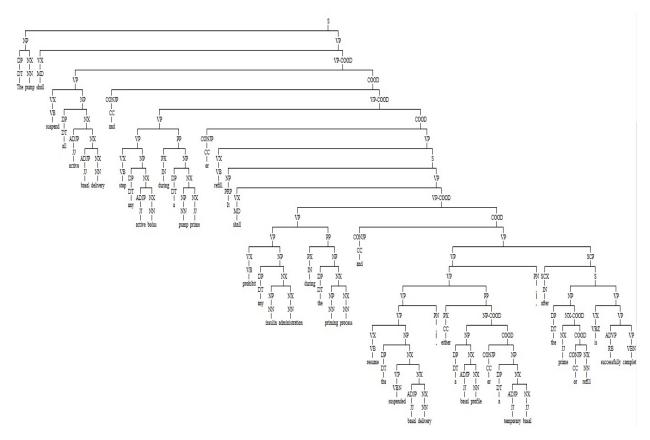

Applying lines 1-14 of APTCER on the requirement in Figure 2.12 gives three TBSs, they are shown in separate red boxes. While the rest of the algorithm (lines 15-38) works on each TBS to find it's AP-list and TC-list. The left sentence has one AP which is "air-line-alarm" and one TC which is "maximum delay time of x minutes". The resulting AP and TC will be saved as a pair. This helps in identify that the AP and TC are correlated, which is used to determine the transition for which the TC should be applied. More specifically, the TC will be applied to a transition from a state in which the corresponding AP is true. Overall the three TBS from Figure 2.12 give the following. AP-list is: 'air-in-line alarm', 'air bubbles larger than y  $\mu$ L', and 'insulin administrations'. TC-list will have one TC: maximum delay time of x seconds which related to the AP of 'air-in-line alarm' as one pair.

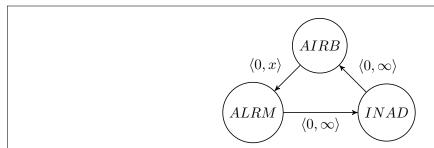

Note that a TBS can correspond to more than one AP and more than one TC. For example, Figure 2.13 shows a TBS that has two APs (in red boxes) and one TC (in a green box).

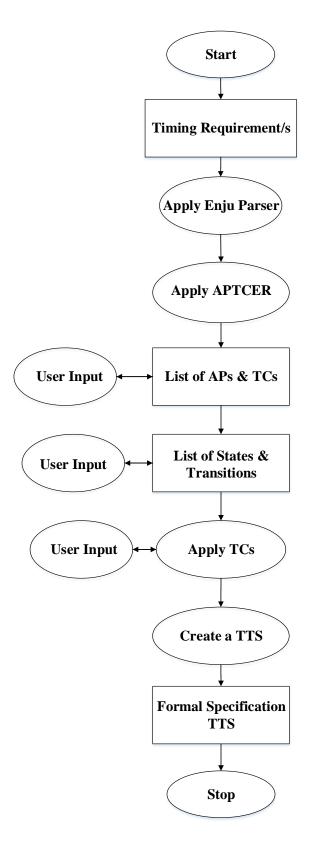

# 2.5.2. High-Level Procedure for Specification Timed Transition System Synthesis

Procedure 6 shows the overall flow for computing the TTSs. A set of natural language timing requirements are input to the procedure. TTS-set is the output of the procedure and will contain the set of timed transition systems that capture the input requirements as a formal model.

TTS-set is initialized to null (line 1). Each timing requirement is input to the Enju parser. The parser gives an xml file as output. A function called Get is used to obtain the xml file into the variable Parse-tree (line 3). The xml output in Parse-tree is subjected to our proposed APTCER, which gives the TBS-list that are pairs of atomic propositions and their related timing constrains lists (line 4). The synthesizing procedure then iterates through all TBSs (line 5) to get thier corresponding pair of APs and TCs (line 6).

AP-lists is subjected to an expert user check, where the APs might be appended, eliminated or revised based on the expert user's domain knowledge (line 7). Some of the APs maybe expressible as a Boolean function of other APs. Therefore, next, a truth table (AP-truth-table) is created, where each row corresponds to an AP from AP-lists and each column also corresponds to an AP from AP-lists (line 8). Each entry in the table is a Boolean value (true or false). Completing the truth table determines the relationship of each AP with the other APs in the AP-lists. The truth

table is completed by the expert user (line 9). TC-list is then checked by the expert user, where some TCs might be appended, eliminated or revised based on the expert user's domain knowledge (line 10).

# Procedure 5 APTCER

```

Require: Parse-tree

1: TBS-list \leftarrow \emptyset;

2: for each Head - Cat \in Head(Parse-tree) do

if Head-Cat = S then

3:

if (Left-Child (S)= NP \vee NP-COOD ) \wedge

4:

(Right-Child (S) = VP) then

TBS = Sub\text{-tree (S)};

5:

for each Child-Head (TBS) do

6:

if Child-Head (TBS) = SCP then

7:

Cut-Sub-tree (SCP);

8:

9:

return TBS;

10:

else

if Child-Head (TBS) = S then

11:

Cut-Sub-tree (S);

12:

return TBS;

13:

TBS-list \leftarrow TBS-list \cup TBS;

14:

15: k \leftarrow \emptyset;

16: for each TBS \in TBS-list) do

17:

K = k + 1;

A \leftarrow \emptyset, B \leftarrow \emptyset;

18:

A = Sub-tree (left-Child (TBS));

19:

AP - list_k \leftarrow \emptyset;

20:

APER 1 (A) \rightarrow AP-list;

21:

AP - list_k \leftarrow AP-list;

22:

B = Sub-tree (Right-Child (TBS));

23:

TC - list_k \leftarrow \emptyset;

24:

APER 1 (B) \rightarrow AP-list;

25:

TC - list_k \leftarrow AP-list;

26:

TBS_k = \langle AP - list_k, TC - list_k \rangle;

27:

28:

TBS-list \leftarrow TBS-list \cup TBS_k;

```