# MITIGATING NONLINEAR EFFECT AND PRESERVING PRIVACY FOR MEMRISTOR BASED ON-CHIP NEURAL NETWORK

A Dissertation

Submitted to the Graduate Faculty

of the

North Dakota State University

of Agriculture and Applied Science

By

Jingyan Fu

In Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY

Major Department: Electrical and Computer Engineering

December 2021

Fargo, North Dakota

## North Dakota State University Graduate School

#### Title

# MITIGATING NONLINEAR EFFECT AND PRESERVING PRIVACY FOR MEMRISTOR BASED ON-CHIP NEURAL NETWORK

| TOR MEMRISTOR BASED ON-CHIE NEURAL NET WORK                                       |                                              |  |

|-----------------------------------------------------------------------------------|----------------------------------------------|--|

| Ву                                                                                |                                              |  |

| Jingyan Fu                                                                        |                                              |  |

|                                                                                   |                                              |  |

| The Supervisory Committee certifies that                                          | this disquisition complies with North Dakota |  |

| State University's regulations and meets the accepted standards for the degree of |                                              |  |

| DOCTOR (                                                                          | OF PHILOSOPHY                                |  |

|                                                                                   |                                              |  |

| SUPERVISORY COMMITTEE:                                                            |                                              |  |

| Dr. Danling Wang                                                                  |                                              |  |

| Chair                                                                             |                                              |  |

| Dr. Qifeng Zhang                                                                  |                                              |  |

| Dr. Sumitha George                                                                |                                              |  |

| Dr. Mijia Yang                                                                    |                                              |  |

|                                                                                   |                                              |  |

|                                                                                   |                                              |  |

| Approved:                                                                         |                                              |  |

| December 13 2021                                                                  | Dr. Renjamin Braaten                         |  |

Date

Department Chair

#### **ABSTRACT**

Memristors offer advantages as a hardware solution for neuromorphic computing, however, their non-ideal property makes the weight update difficult and reduces the accuracy of a neural network. Also, a large amount of personal data has raised great concern about the privacy preservation of neural networks. Thus, the performance of memristor-based neural networks gets worse when considering non-ideal property and introducing a privacy preservation mechanism. This dissertation focuses on improving the performance of a memristor-based privacy-preserving neural network.

A piecewise linear (PL) method is proposed to mitigate the nonlinear effect of memristors by calculating the weight update parameters along a piecewise line, which reduces errors in the weight update process. It mitigates the nonlinearity impact without reading the precise conductance of the memristor in each updating step, thereby avoiding complex peripheral circuits. What's more., the PL method is proved to be an effective technique that can prevent accuracy loss and increase privacy preservation space for privacy-preserving ANN. Also, we propose a Noise Distribution Normalization (NDN) method to add Gaussian distributed noise through hardware implementation, thereby achieving differential privacy in edge AI. Instead of using traditional algorithmic noise-insertion methods, we take advantage of inherent cycle-to-cycle variations of memristors during the weight-update process as the noise source, which does not incur extra software or hardware overhead.

#### ACKNOWLEDGMENTS

Thanks to all the people that supported my effort on this dissertation.

I would like to express my deepest gratitude to my advisor Dr. Jinhui Wang, who read my numerous revisions, helped make some sense of the confusion, and persistently encouraged me. and conveyed the spirit and guidance required for the research. Also, I am deeply indebted to my advisors Dr. Danling Wang, Dr. Scott C. Smith, and Dr. Sudarshan K. Srinivasan. Without their invaluable guidance this project would not have been possible. I would also like to thank Dr. Qifeng Zhang, Dr. Mijia Yang, Dr. Sumitha George, who shared me expertise and valuable guidance.

I am extremely grateful to Dr. Khang Hoang. I am extremely thankful and indebted to him for supporting, sharing and encouragement. I am also grateful to all staff at Center for Computationally Assisted Science and Technology (CCAST). I would also like to thank Fred Haring in R2 at Center for Nanoscale Science and Engineering of North Dakota State University.

## **DEDICATION**

To my family.

## TABLE OF CONTENTS

| ABSTRACT                                                                                                                 | iii |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                                                                                          | iv  |

| DEDICATION                                                                                                               | v   |

| LIST OF TABLES                                                                                                           | x   |

| LIST OF FIGURES                                                                                                          | xi  |

| LIST OF ABBREVIATIONS                                                                                                    | xiv |

| 1. INTRODUCTION                                                                                                          | 1   |

| 1.1. Background                                                                                                          | 1   |

| 1.2. Research Objective                                                                                                  | 3   |

| 1.3. Contributions                                                                                                       | 5   |

| 1.4. Organization                                                                                                        | 7   |

| 2. RELATED WORK                                                                                                          | 10  |

| 2.1. Related Work on Mitigating Nonlinear Effect of Memristive Synaptic Device                                           | 10  |

| 2.2. Related Work on Memristor-Based Neuromorphic Hardware Improvement for Privacy-Preserving Neural Network             | 12  |

| 2.3. Related Work on Memristor Based Variation Enabled Differentially Private Learning Systems for Edge Computing in IoT | 13  |

| 3. PRELIMINARIES                                                                                                         | 15  |

| 3.1. Artificial Neural Networks (ANN)                                                                                    | 15  |

| 3.1.1. Neural Networks                                                                                                   | 15  |

| 3.1.2. SGD Algorithm                                                                                                     | 18  |

| 3.1.3. Long-term Potentiation (LTP) and Long-term Depression (LTD)                                                       | 19  |

| 3.2. Memristors                                                                                                          | 19  |

| 3.2.1. Synaptic Device                                                                                                   | 21  |

| 3.2.2. Nonlinearity of Memristors                                                                                        | 23  |

| 3.2.3. Cycle-to-cycle Variation of Memristors                                              | 25 |

|--------------------------------------------------------------------------------------------|----|

| 3.2.4. Artificial Neural Networks (ANN) and Memristor                                      | 26 |

| 3.3. Differential Privacy                                                                  | 28 |

| 3.4. Differentially Private SGD Algorithm (DP-SGD)                                         | 31 |

| 4. MITIGATING NONLINEAR EFFECT OF MEMRISTIVE SYNAPTIC DEVICE FOR NEUROMORPHIC COMPUTING    | 33 |

| 4.1. Introduction                                                                          | 33 |

| 4.2. Methodology                                                                           | 35 |

| 4.3. Application on Digits Image Recognition                                               | 37 |

| 4.3.1. Split Selection Strategies and 2/3/4-segment Models                                 | 37 |

| 4.3.2. Working Flow of the PL Method                                                       | 38 |

| 4.4. Results and Discussion                                                                | 44 |

| 4.4.1. Working Flow of the PL Method                                                       | 45 |

| 4.4.2. Stability of Recognition Accuracy                                                   | 48 |

| 4.4.3. Impact of LTD and LTP                                                               | 49 |

| 4.4.4. Impact of Split Selection Strategies                                                | 50 |

| 4.4.5. Impact of NL                                                                        | 52 |

| 4.4.6. Storage and Pulses Cost of PL Method                                                | 52 |

| 4.4.7. Variations of Memristors                                                            | 54 |

| 4.4.8. Different Neural Network                                                            | 55 |

| 4.4.9. The PL Method and Other Works                                                       | 56 |

| 4.5. Conclusion                                                                            | 57 |

| 5. MEMRISTOR-BASED NEUROMORPHIC HARDWARE IMPROVEMENT FOR PRIVACY-PRESERVING NEURAL NETWORK | 58 |

| 5.1. Introduction                                                                          | 58 |

| 5.2. Methodology                                                                           | 60 |

| 5.2.1. Memristors                                                                                      | 60 |

|--------------------------------------------------------------------------------------------------------|----|

| 5.2.2. Differentially Private Transformation                                                           | 60 |

| 5.3. Experimental Evaluation                                                                           | 61 |

| 5.3.1. Models                                                                                          | 61 |

| 5.3.2. Impact of Private Perturbation                                                                  | 62 |

| 5.3.3. Models Stability                                                                                | 66 |

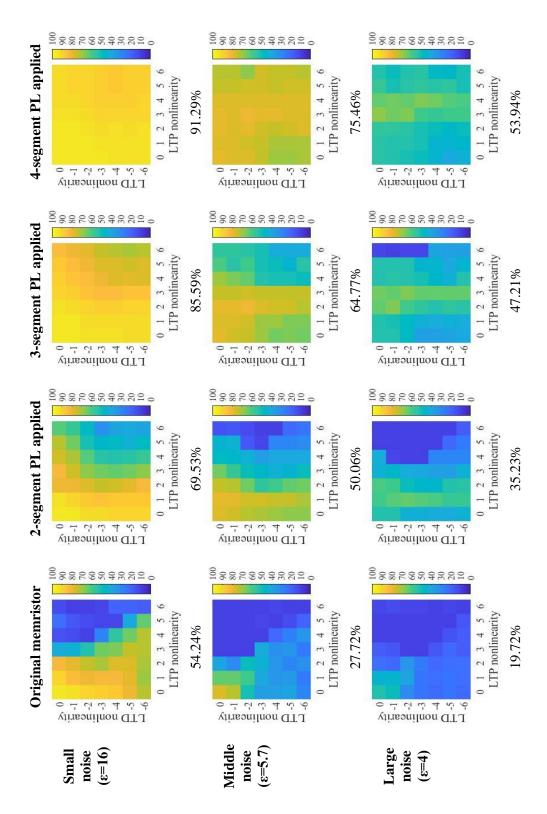

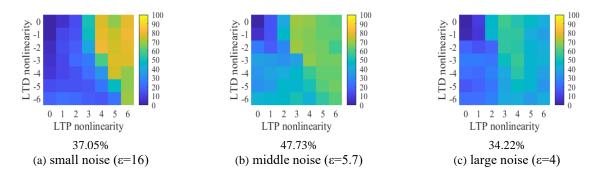

| 5.3.4. Privacy-preserving Space for Various Nonlinearity                                               | 69 |

| 5.3.5. Cost Analysis                                                                                   | 72 |

| 5.3.6. Variations of Memristors                                                                        | 72 |

| 5.3.7. Comparison with Other Works                                                                     | 74 |

| 5.4. Conclusion                                                                                        | 75 |

| 6. MEMRISTOR BASED VARIATION ENABLED DIFFERENTIALLY PRIVATE LEARNING SYSTEMS FOR EDGE COMPUTING IN IOT | 76 |

| 6.1. Introduction                                                                                      | 76 |

| 6.2. Gaussian Distribution of Cycle-to-Cycle Variation                                                 | 79 |

| 6.2.1. Mathematical Expression of Cycle-to-Cycle Variation                                             | 79 |

| 6.2.2. Cycle-to-Cycle Variations of Positive and Negative Pulse Pairs                                  | 80 |

| 6.3. Noise Injection in Accordance with DP                                                             | 81 |

| 6.3.1. Noise Distribution Normalization (NDN) Method                                                   | 82 |

| 6.3.2. Privacy Analysis                                                                                | 82 |

| 6.4. Case Study and Discussions                                                                        | 84 |

| 6.4.1. Implementation of DP-SGD via Hardware in Edge AI                                                | 84 |

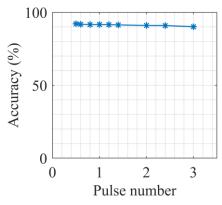

| 6.4.2. Results of Clipping NDN                                                                         | 87 |

| 6.4.2. Results of NDN Method                                                                           | 88 |

| 6.4.3. Comparison with Existing Work                                                                   | 90 |

| 6.4.4. Nonlinearity              | 91 |

|----------------------------------|----|

| 6.4.5. Scalability and Endurance | 93 |

| 6.5. Conclusions                 | 94 |

| 7. CONCLUSIONS                   | 96 |

| REFERENCES                       | 98 |

## LIST OF TABLES

| <u>Table</u> |                                                                              | <u>Page</u> |

|--------------|------------------------------------------------------------------------------|-------------|

| 1.           | Cost and Overall Accuracy with the PL Method in Different Cases <sup>a</sup> | 53          |

| 2.           | Variations Cases                                                             | 55          |

| 3.           | Recognition Accuracy with Variations.                                        | 55          |

| 4.           | Recognition Accuracy of Networks with Different Neurons.                     | 56          |

| 5.           | The Comparison of the State-of-art.                                          | 56          |

| 6.           | Cost and Average Accuracy with Different Models.                             | 71          |

| 7.           | Recognition Accuracy with Different Variations.                              | 73          |

| 8.           | The Comparison of the State-of-art.                                          | 74          |

| 9.           | Sigma Parameter of Cycle-to-Cycle Variation*                                 | 89          |

| 10.          | The Comparison with State-of-the-Art.                                        | 91          |

| 11.          | Recognition Accuracy with NDN Method and Nonlinearity.                       | 92          |

| 12.          | Total Power of Memristor-Based Array in Learning Device.                     | 93          |

| 13.          | Recognition Accuracy with Various Failure Rates                              | 94          |

| 14.          | Recognition Accuracy with Conductance Drifting.                              | 94          |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.            | Artificial neural network                                                                                                                                                                                                                                                                                                                                                                                               | 17          |

| 2.            | Neural network between two layers. $V_i$ , $G_{i,j}$ , and $I_j$ represent the input signal in $i^{th}$ neuron, the weight of the synapses in $j^{th}$ neuron of output layer and $i^{th}$ neuron in input layer, and the output sum that represent the dot product result of $V$ and $G$ , respectively.                                                                                                               | 18          |

| 3.            | The four fundamental two-terminal circuit elements                                                                                                                                                                                                                                                                                                                                                                      | 20          |

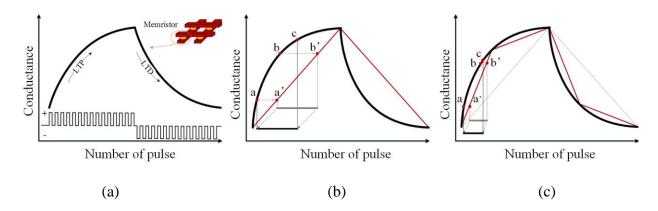

| 4.            | The conductance change (weight updating) curve. (a) Conductance changes with identical input pulses. (b) Weight updating process based on linear line. (c) Weight updating process based on a piecewise line.                                                                                                                                                                                                           | 24          |

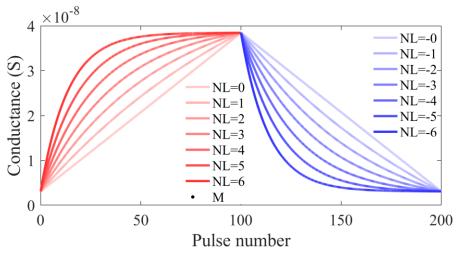

| 5.            | Conductance change curves under various nonlinearity of LTP and LTD                                                                                                                                                                                                                                                                                                                                                     | 25          |

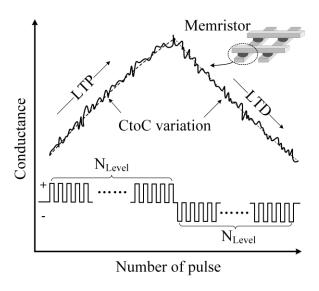

| 6.            | Long-term potentiation process (LTP), long-term decrease process (LTD), and cycle-to-cycle variation of a memristor. $N_{\text{Level}}$ represents the number of conductance states of a memristor.                                                                                                                                                                                                                     | 26          |

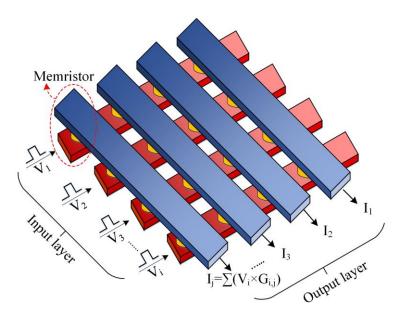

| 7.            | Hardware implementation of neural networks using memristor crossbar. $V_i$ , $G_{i,j}$ , and $I_j$ represent the input signal in $i^{th}$ row, the conductance of the memristor in $j^{th}$ column and ith row, and the output current that represent the dot product result of $V$ and $G$ , respectively.                                                                                                             | 27          |

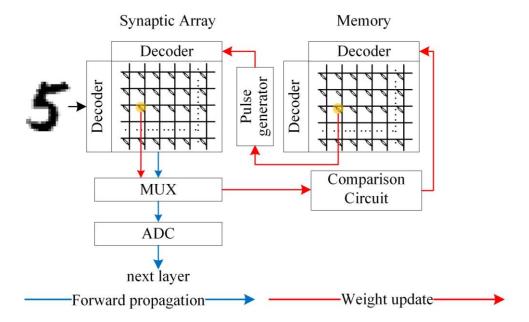

| 8.            | Block diagram of circuit flow of a three-layer ANN                                                                                                                                                                                                                                                                                                                                                                      | 28          |

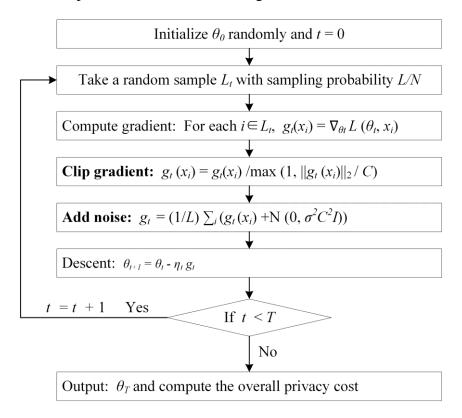

| 9.            | Outline of DP-SGD. Symbols and parameters: input dataset, weights $\theta$ , loss function $L(\theta)$ , gradient $g$ , learning rate $\eta_t$ , noise scale $\sigma$ , group size $L$ , gradient norm bound $C$ , total weight update step $T$ , the square root of the largest eigenvalue of the matrix $gt(x_i)^*gt(x_i)$ , $  gt(x_i)  _2$ , where $gt(x_i)^*$ denotes the conjugate transpose of $  gt(x_i)  _2$ . | 32          |

| 10.           | Conductance change diagram. (a) LTP, (b) LTD, (c)2-segment model, (d) 3-segment model.                                                                                                                                                                                                                                                                                                                                  | 36          |

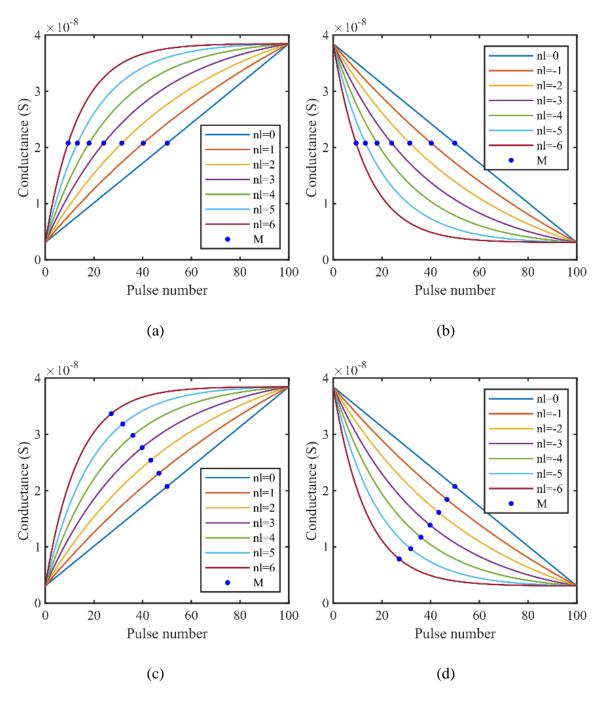

| 11.           | 2-segment model. (a) LTP and middle split-point, (b) LTD and middle split-point, (c) LTP and slope split-point, (d) LTD and slope split-point                                                                                                                                                                                                                                                                           | 41          |

| 12.           | 3-segment model. (a) LTP and middle split-point, (b) LTD and middle split-point, (c) LTP and slope split-point, (d) LTD and slope split-point                                                                                                                                                                                                                                                                           | 42          |

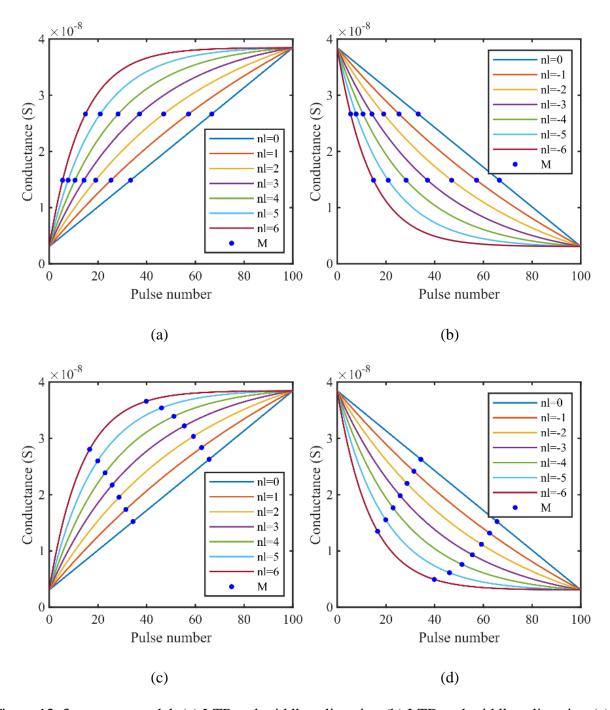

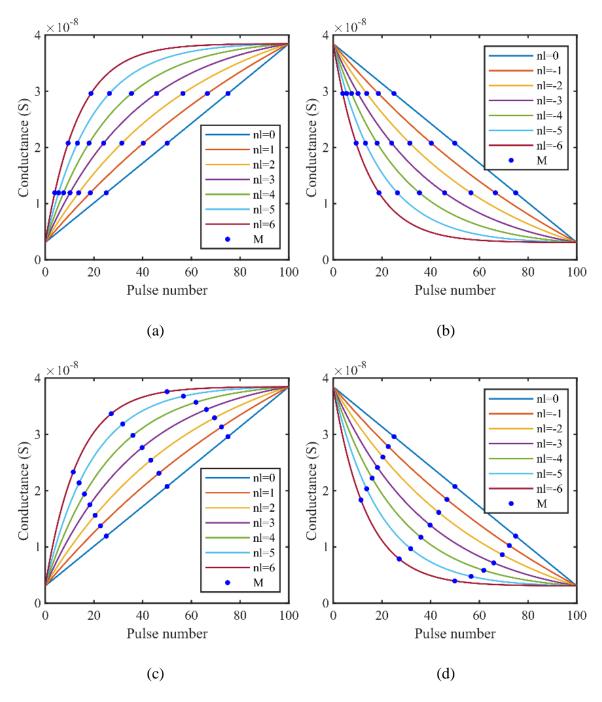

| 13.           | 4-segment model. (a) LTP and middle split-point, (b) LTD and middle split-point, (c) LTP and slope split-point, (d) LTD and slope split-point                                                                                                                                                                                                                                                                           | 43          |

| 14. | Algorithm of Split Points M with Slope Strategy                                                                                                                                                                                                                                                            | 44 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

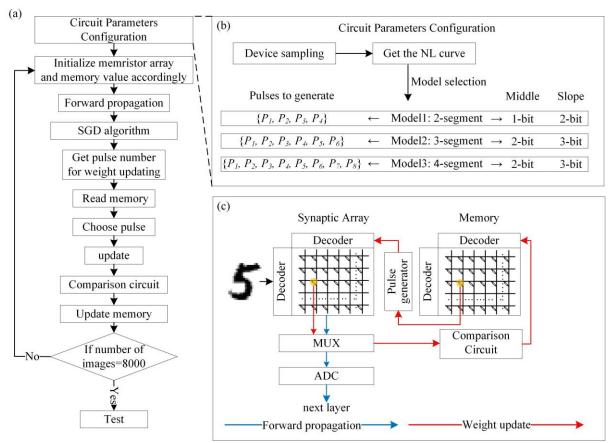

| 15. | (a) Flow chart of hardware-based neural network, (b) Circuit parameters configuration, (c) Block diagram of circuit flow.                                                                                                                                                                                  | 45 |

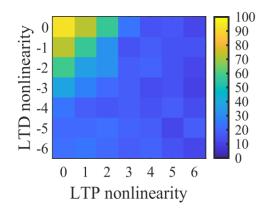

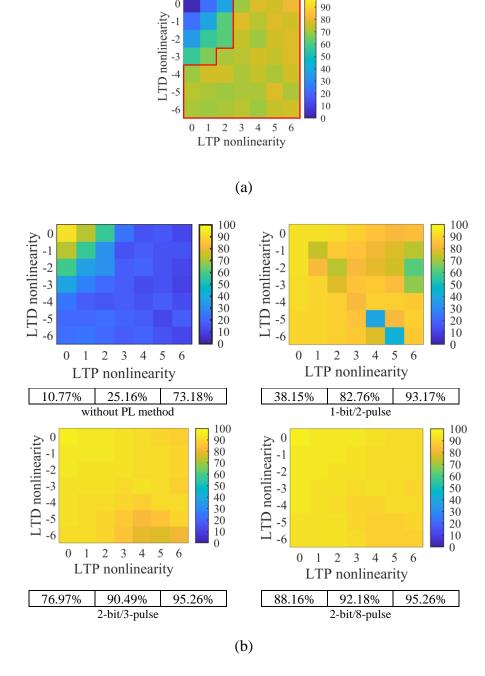

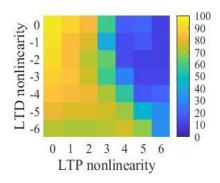

| 16. | Original recognition accuracy for memristors with nonlinearity property. Minimum accuracy is 10.77%. Overall (Average) accuracy is 25.16%. Maximum accuracy (with NL) is 73.18%. Without nonlinearity accuracy (NL (0,0)) is 95.55%                                                                        | 46 |

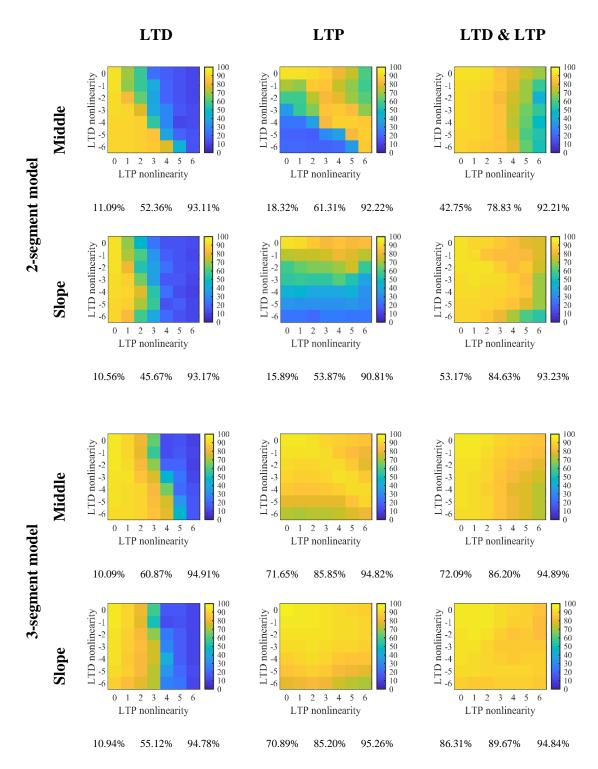

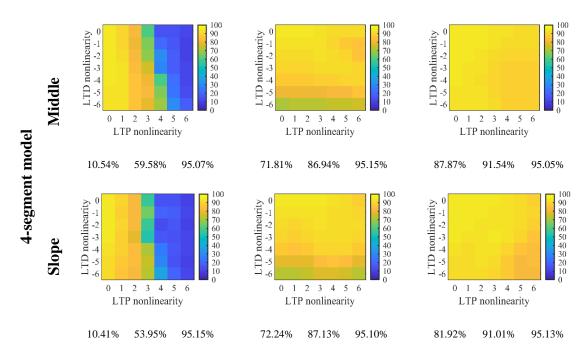

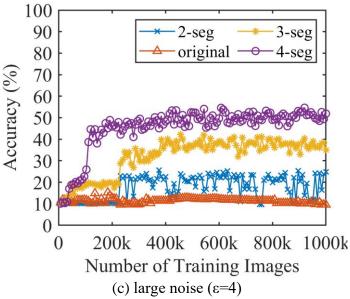

| 17. | The prediction accuracy of digit recognition with PL method in different configurations. The numbers under each figure are minimum accuracy, overall (average) accuracy, and maximum accuracy.                                                                                                             | 47 |

| 18. | The recognition accuracy of the MNIST handwriting digits when the nonlinearity is NL: (6/-6) that is considered as the worst nonlinearity case                                                                                                                                                             | 48 |

| 19. | (a) The improvement of recognition accuracy. The red outline shows the cases that have accuracy improvement over 70%. (b) The highest accuracy achievement under the same cost. The number under each figure means minimum accuracy, overall accuracy, and maximum accuracy (except ideal case NL: (0,0)). | 51 |

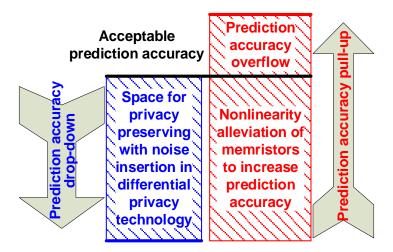

| 20. | Concept of memristor-based neuromorphic hardware improvement for privacy-preserving ANN.                                                                                                                                                                                                                   | 59 |

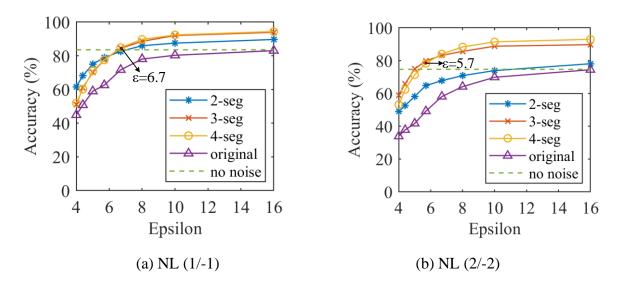

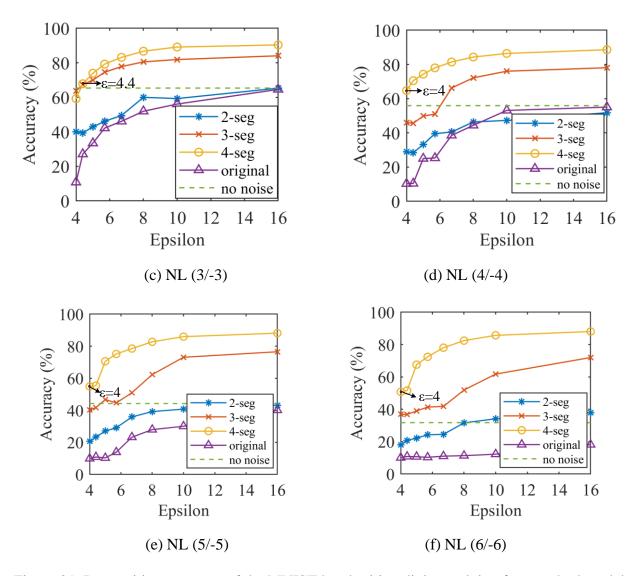

| 21. | Recognition accuracy of the MNIST handwriting digits applying four method models with different private perturbation. The NL $(x/-y)$ means the LTP nonlinearity of memristor is x and the LTD nonlinearity of memristor is y                                                                              | 63 |

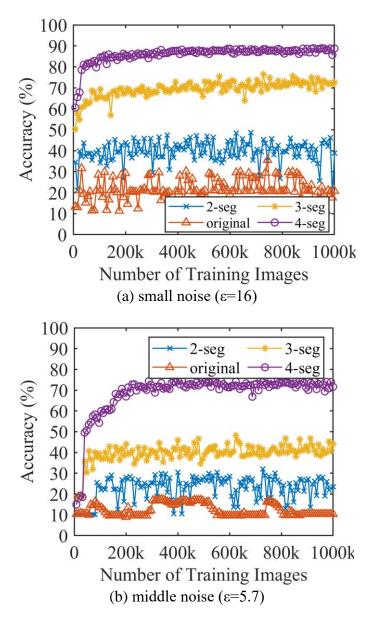

| 22. | Recognition accuracy of the MNIST handwriting digits with the training images when the nonlinearity is NL (6/-6) that is considered as the worst nonlinearity case                                                                                                                                         | 65 |

| 23. | Recognition accuracy of the MNIST handwriting digits without the privacy-preservation and PL method. The average accuracy of the 49 memristors' nonlinearity cases is 55.97%                                                                                                                               | 67 |

| 24. | The recognition accuracy of memristor-based ANN with different models for 49 nonlinearity cases of memristor.                                                                                                                                                                                              | 68 |

| 25. | Recognition accuracy improvement of 4-segment LO model. The average accuracy improvement of each figure is shown under each figure.                                                                                                                                                                        | 70 |

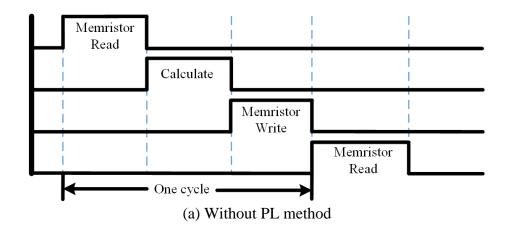

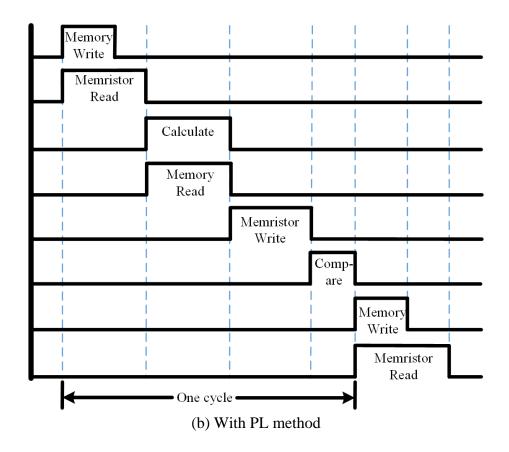

| 26. | One cycle timing schematic in weight update process. (a) Without PL method, (b) With PL method. The memory represents the added memory component and the memristor represents the memristor that acts as a synapse in neural network                                                                       | 70 |

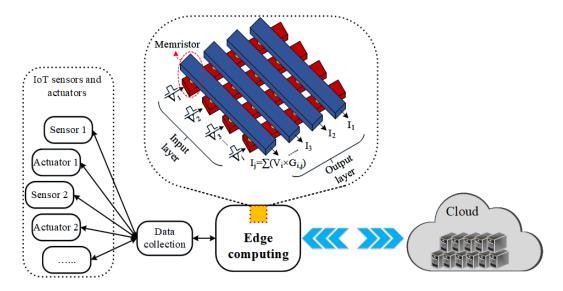

| 21. | and I <sub>j</sub> represent the input signal in the i <sup>th</sup> row, the conductance of the memristor in the j <sup>th</sup> column and ith row, and the output current that represents the dot product result of V and G, respectively.                                                                                                                                | 78 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

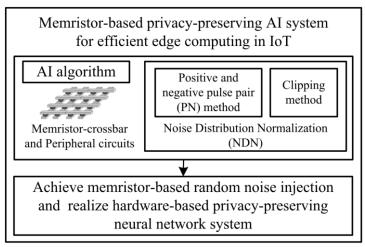

| 28. | Outline of the proposed methods.                                                                                                                                                                                                                                                                                                                                             | 84 |

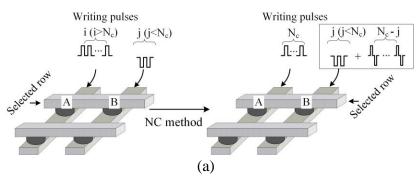

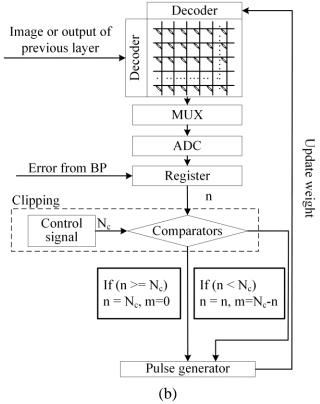

| 29. | Workflow of the NDN method, where n represents the number of pulses that are used to update a weight and m represents the number of positive and negative pulse pairs. (a) Example: after applying the NDN method, for memristor A $n=N_c$ , $m=0$ ; for memristor B, $n=j$ , $m=N_{c-j}$ . (b) Hardware implementation flow of the Noise Distribution Normalization method. | 86 |

| 30. | Recognition accuracy of MNIST under various clip boundaries                                                                                                                                                                                                                                                                                                                  | 88 |

| 31. | Recognition accuracy of MNIST handwriting digits under various noise levels                                                                                                                                                                                                                                                                                                  | 89 |

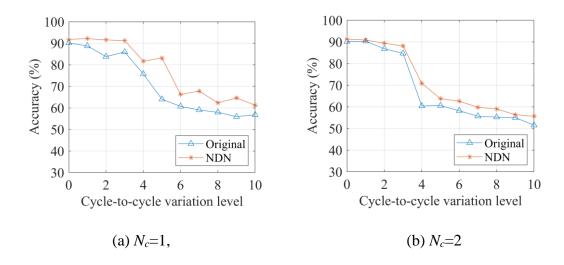

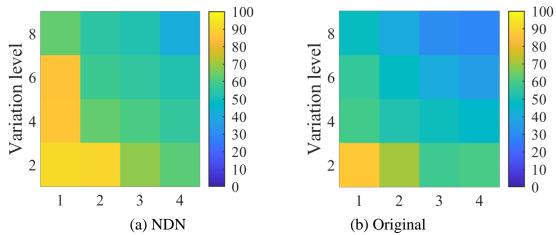

| 32. | Recognition accuracy of MNIST handwriting digits under various noise levels and different number of pulse pairs: (a) using NDN method, where the x-axis represents the number of pulse pairs, N <sub>c</sub> ; (b) Original case, where the x-axis has the same noise scale as (a).                                                                                          | 90 |

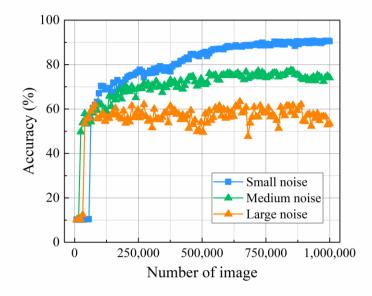

| 33. | Recognition accuracy of training process using NDN method under three noise levels, where σ for small noise, medium noise, and large noise equals 3%, 6%, and 12%, respectively.                                                                                                                                                                                             | 90 |

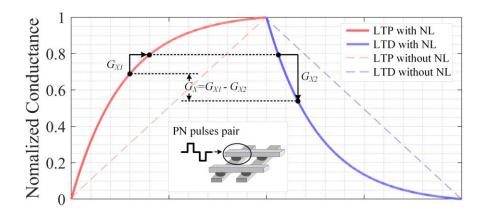

| 34. | Nonlinearity effect on conductance modulation of memristors                                                                                                                                                                                                                                                                                                                  | 92 |

## LIST OF ABBREVIATIONS

| AI               | Artificial Intelligence                                 |

|------------------|---------------------------------------------------------|

| ALU              | Arithmetic Logic Unit                                   |

| ANNs             | Artificial neural networks                              |

| CMOS             | Complementary Metal-Oxide-Semiconductor                 |

| G <sub>max</sub> | Maximum Conductance                                     |

| G <sub>min</sub> | Minimum Conductance                                     |

| IoT              | Internet of Things                                      |

| LTD              | Long-Term Depression                                    |

| LTP              | Long-Term Potentiation                                  |

| MLP              | Multilayer Perceptron                                   |

| MNIST            | Modified National Institute of Standards and Technology |

| ReRAM            | Resistive Random-Access Memory                          |

| SGD              | Stochastic Gradient Descent                             |

| VLSI             | Very Large-Scale Integration                            |

#### 1. INTRODUCTION

#### 1.1. Background

Device scaling on the CMOS technology that effectively benefits the cost, speed, and power efficiency of Integrated Circuits (ICs), has driven the boom of the computing systems over the past several decades. Unfortunately, the increasing physical restrictions such as thermodynamic limits including quantum tunneling [1] make COMS device scaling reach a plateau, which suppresses the further progress of computing systems in large data centers or the Cloud, and also obstruct the fast deployment of sensors and actuators for the Internet of Things (IoT) [2]. Meanwhile, neuromorphic computing using bio-inspired learning algorithms has emerged and achieved tremendous success. However, due to the separated computation unit and memories [3], conventional von Neumann-based computing platform results in insufficient bandwidth and overlarge power consumption, particularly for the fast training and/or classification tasks in neuromorphic computing, such as real-time online recognition. Therefore, new synapse devices and technologies with remarkable performance and less cost are urgently needed.

Memristors are one of such promising devices. A memristor is an analog device to exploit the multilevel conductance states, to regulate the flow of electrical current, and to store the amount of charge that has previously flowed through it [4, 5]. In a memristor-based neuromorphic computing platform, memristors are connected as neuron devices that implement the function of the Sum of Product (SOP). Weight update depends on the transition between different conductance states in memristors, which is typically triggered by voltage pulses. Specifically, according to the programmed voltage pulses, the conductance of memristors positively and negatively changes, enabling weight increase and decrease, respectively [3]. As a result, it can not only act as the non-volatile memory, but realize the in-memory calculation which brings high potential to implement

neural networks in hardware. Different from traditional CMOS-based hardware, such as Field Programmable Gate Array (FPGA), Application Specific Integrated Circuit (ASIC), Graphics Processing Unit (GPU), and Tensor Processing Unit (TPU), the memristor-based in-memory computing architecture breaks the memory wall that results from the Von Neumann architecture, thereby achieving at least a 7× reduction of active power for implementing a basic neuron function [6]. Also, memristors have better CMOS process compatibility as compared with emerging technologies such as quantum computing, molecular computing, quantum dots, and spin-wave devices. However, memristors are not flawless and intrinsically suffering from their variability issues. The physical mechanism of the conductance modulation in most prospective synaptic devices is typically an ionic reconfiguration process based on electro/thermo-dynamics [7, 8]. This atomic-level random process is responsible for unavoidable variations including nonlinearity, device-to-device, cycle-to-cycle, and ON/OFF conductance variations [9]. The nonlinearity property makes it challenging to determine a proper width or amplitude of input signals for achieving the desired conductance of memristors. The cycle-to-cycle variations result in the different updated conductance when the same updating signal in different updating cycles is applied to a memristor, even when the initial conductance is the same.

Recent years have witnessed significant progress in mobile devices and wireless sensor networks, creating unprecedented opportunities to deploy deep learning for smart IoT applications. However, when deep learning algorithms work on the edge for human-related applications, IoT devices will collect data, which in some cases may contain quite personal and high-value user information, therefore raising significant concerns regarding information privacy. It is thus possible for the private data to be misused, or to be hacked by outside attacks. Therefore, some sort of privacy protection method is required to guarantee a strong notion of privacy, while

preserving learning accuracy. Differential privacy [10] is one of the most popular technologies for privacy-preserving deep learning, realized by introducing perturbations. Differential privacy (DP) provides a mathematical constraint for the privacy loss associated with any data release from a statistical database. However, differentially private learning systems not only need to train complex models, but also must perform an additional computation for noise insertion as a protective mechanism to datasets, models, and algorithms [11]. Such a high-cost training process undoubtedly challenges traditional CMOS based hardware technology, and hinders development of deep learning, especially for power-sensitive and resource-limited edge computing in IoT systems. Therefore, instead of traditional CMOS based hardware technology, a memristor based differentially private learning system, with its low computation and storage cost, is an excellent candidate for edge AI.

Thus, this dissertation focuses on improving the performance of memristor based privacy preserving neural network.

#### 1.2. Research Objective

Memristor-based neuromorphic computing is such a flexible and attractive technology to meet the increasing needs of data processing [4, 5]. A memristor is a device with only three layers structure that can not only realize desirable device properties such as sub-10 nm feature sizes [12], sub-nanosecond switching speed [13, 14], long write-erase endurance [15], and nanoamperes programming energy [16], but also exploit multilevel conductance states [5]. However, memristors are not flawless, and intrinsically suffer from variability issues. The physical mechanism of the conductance modulation in most prospective synaptic devices is typically an ionic reconfiguration process based on electro/thermo-dynamics [7, 8]. This atomic-level random process is responsible for unavoidable variations including nonlinearity, device-to-device, cycle-to-cycle, and ON/OFF

conductance variations [9]. These non-ideal properties extremely degrade the performance of a memristor-based circuit. For instance, the nonlinearity makes it challenging to determine a proper width or amplitude of input signals for achieving the desired conductance of memristors. It is reported that the linear conductance change is the major requirement of memristor-based neuromorphic computing to realize high accuracy for online learning [3]. Four state-of-the-art memristors in literature – Ag:a-Si [17], TaO<sub>x</sub>/TiO<sub>2</sub> [18], PCMO [19], and AlOx/HfO<sub>2</sub> [20] are all characterized by device nonlinearity. As discussed in [9, 17], the accuracy of recognition based on Ag:a-Si with nonlinearity decreases over 20% compared to without nonlinearity. Therefore, firstly, my research objective is to propose new techniques that can mitigate the negative impact of memristor's variations, especially the nonlinearity variation.

To build a memristor-based neuromorphic computing system, another non-negligible point is privacy protection because usually the network is built from a large amount of private data training. Effective privacy protection technologies of memristor-based neuromorphic system are urgently needed A privacy preserving method is to introduce a randomized noise mechanism for differential privacy technology to quantify the protection ability. However, noisy and distorted data would lead to a degradation of recognition accuracy in ANN. Accordingly, solutions to balance privacy preserving and recognition accuracy are indeed needed. Therefore, secondly, my research objective is applying our proposed techniques on a memristor based privacy preserving neural network to counteract recognition degradation due to noise injection.

Apart from the nonlinearity of memristors, which is mentioned above, the other non-ideal properties of memristors also degrade the performance of a memristor-based neuromorphic computing circuit. These properties include device-to-device variation, cycle-to-cycle variation, maximum conductance variation, and minimum conductance variation. Although these non-ideal

properties influence learning precision of a memristor-based system, such variations can also be considered as inherent resources for noise generation. Also, the privacy preserving method needs to introduce such randomized noise. Therefore, a promising way is to utilize variations of memristor. By this method, it is possible to add Gaussian noise distribution to a system without adding computational complexity and introducing extra hardware. Therefore, thirdly, my objective is to convert the negative impact of memristor's cycle-to-cycle variation into a positive impact by utilizing the memristor for privacy-preserving neural networks.

#### 1.3. Contributions

This dissertation focuses on improving the performance of memristor based privacy preserving neural network.

First, a piecewise linear (PL) method is proposed to mitigate the nonlinear effect of memristors by calculating the weight update parameters along a piecewise line, which reduces errors in the weight update process. It mitigates the nonlinearity impact without reading the precise conductance of the memristor in each updating step, thereby avoiding complex peripheral circuits. This method makes the following contributions:

- A PL method is proposed to effectively mitigate the impact of memristor's nonlinearity property. Without reading precise conductance of memristors, the PL method makes weight update process along a piecewise line and the detailed working flow is presented.

- To explore the PL method and its configuration, the relations among the recognition accuracy, number of segments, split selection strategies, and nonlinearity behaviors are investigated through the Modified National Institute of Standards and Technology (MNIST) database [21] based on simulation platform.

- Based on various configuration models provided by the PL method, the tradeoff analysis is conducted to reduce the cost by selecting an appropriate model.

- By thorough evaluation, the effectiveness of the PL method is verified even with various variations including device-to-device variation, cycle-to-cycle variation, maximum or minimum conductance variation, and ON/OFF ratio variation.

What's more, the PL method is proved to be an effective technique that can prevent accuracy loss and increase privacy preservation space for privacy-preserving ANN. This investigation makes the following contributions:

- A method for mitigating the nonlinearity impact in memristor-based privacypreserving ANN. To mitigate the impact of memristor's nonlinearity property, an effective,

hardware-based PL method with low circuit overhead is proposed, which makes the neuromorphic

system become more accurate and applicable for ANN application.

- A mechanism enhancing the immunity of memristor-based privacy-preserving ANN to nonlinearity property of memristor device. By applying the PL method under eight groups of private perturbations that follow differential privacy theory, the recognition accuracy of ANN is proved to get negligible degradation or even get increase than before.

- Thorough evaluation. We evaluate the proposed method on standard image classification tasks [21] and conduct over 1,500 simulations that include 4 models, 8 groups of privacy perturbations, and 49 nonlinearity cases.

- The tradeoff analysis. The PL method provides a variety of configuration models, and we discuss how to reduce the cost by selecting the appropriate model while meeting the privacy and accuracy requirements based on the actual device.

Also, we propose a Noise Distribution Normalization (NDN) method to add Gaussian distributed noise through hardware implementation, thereby achieving differential privacy in edge AI. Instead of using traditional algorithmic noise-insertion methods, we take advantage of inherent cycle-to-cycle variations of memristors during the weight-update process as the noise source, which does not incur extra software or hardware overhead. This method makes the following contributions:

- A hardware solution that breaks the limitations of traditional software-based noise-adding mechanisms of DP. A memristor-based hardware solution is proposed for differentially private learning systems that does not require additional circuitry. In this paper, the positive and negative pulse pair (PN) method is used to generate adjustable Gaussian noise, satisfying the DP constraint. The proposed method transforms non-beneficial cycle-to-cycle variations into a valuable measure for privacy protection.

- Methods that address Differentially Private Stochastic Gradient Descent (DP-SGD) by hardware implementation. The Clipping method is proposed to avoid the L2 norm calculation of gradient matrices. A combination of the PN method and clipping method, called Noise Distribution Normalization (NDN) method, is proposed to implement the DP mechanism.

- Privacy analysis and performance evaluation. Privacy analysis is conducted to verify the effectiveness of proposed methods. Furthermore, to illustrate the performance of each method, a comprehensive suite of simulations has been conducted.

#### 1.4. Organization

This dissertation is organized into 7 chapters. Chapter 2 introduces related work on mitigating nonlinear effect of memristive synaptic device, related work on improving performance of memristor based neuromorphic hardware for privacy preserving neural network, and related

work on improving performance of memristor based variation enabled differentially private learning systems for edge computing in IoT.

Chapter 3 introduces the preliminaries about memristor and its property, differential privacy, and neural network, which will provide the foundation for the rest of the dissertation.

Chapter 4 introduces a new technique that uses pulses programming method to update the weight, following the nonlinear curve of memristors, thereby enhancing the accuracy of the learning algorithms. It mitigates the nonlinearity impact without reading the precise conductance of the memristor in each updating step, thereby avoiding complex peripheral circuits. The effectiveness of the proposed PL method with respectively 2-segment, 3-segment, and 4-segment models in two split selection strategies is investigated and the impact of various variations are considered.

Chapter 5 applies the proposed method in Chapter 3 to enable privacy-preserving ANN without accuracy degradation. The effectiveness of the proposed PL method with respectively 2-segment, 3-segment, and 4-segment models is investigated. The results show that under different nonlinearity and different perturbation noise required by differential privacy theory, the PL method can increase the recognition accuracy of MNIST handwriting digits by 39.67% on average, which provides more space and margin for privacy-preserving technology.

Chapter 6 introduces a Noise Distribution Normalization (NDN) method to add Gaussian distributed noise through hardware implementation, thereby achieving differential privacy in edge AI. Instead of using traditional algorithmic noise-insertion methods, we take advantage of inherent cycle-to-cycle variations of memristors during the weight-update process as the noise source, which does not incur extra software or hardware overhead. In one case study, the proposed method realizes ultra-low-cost DP-SGD (Differentially Private Stochastic Gradient Descent) for edge AI

in IoT systems, achieving a 3.5% to 15.5% average recognition accuracy improvement under different noise levels, as compared with a baseline mechanism.

Chapter 7 summarizes the major conclusions of this dissertation and suggests a direction for future research.

#### 2. RELATED WORK

To optimize the performance of a memristor-based privacy preserving neural network, researchers propose various techniques addressing the issues that include nonlinear effect of memristive synaptic device, privacy preserving neural network, and cycle-to-cycle variation effect of memristive synaptic device. This chapter includes related work on these topics.

#### 2.1. Related Work on Mitigating Nonlinear Effect of Memristive Synaptic Device

For analog applications of the memristor technology, the intrinsic nonlinearity property causes different conductance changes even with the same voltage pulse. Such nonlinear characteristic is also one of the most undesirable non-ideal factors for neuromorphic computing [9, 22-25]. To mitigate the impact of nonlinearity property, investigations have generally proceeded in the following three aspects.

The first aspect is to change the device structure by manufactural modification in order to eliminate nonlinearity property. For example, a thermal enhanced layer is added to confine heat in the switching layer to the HfO<sub>x</sub> RRAM device [26]. Another solution is to introduce an ion-diffusion limiting layer for the TiN/TaO<sub>x</sub> RRAM device [27]. A more effective way is to utilize a charge trap layer to a gated Schottky diode in order to cancel the nonlinearity factor [28]. Although those devices can achieve relatively better linear property, they may ignore the other important features designated for the neuromorphic computing, such as the ON/OFF ratio and endurance characteristics. For instance, the reconfigurable gated Schottky diode has better linearity, but with low ON/OFF ratio [18, 28], which limits its application as an analog synapse. Moreover, nonlinearity is widespread and intrinsic in almost all memristors. Due to the implementation cost consideration, it is unfeasible nor impractical to create a new manufacturing method to mitigate

nonlinearities for each kind of memristor. As a result, novel effective and feasible approaches are necessary to conduct a synaptic operation.

A more universal aspect is to control the conductance change with the current control, time-domain control, and the flux- and charge-domain control. The current control mechanisms are based on transistor gate voltage and time duration in the configuration of one transistor and one memristor [29, 30]. The flux- and charge-domain control method describes device state as a function of flux or charge and adjusts the device state according to quantization of the flux or charge [31, 32]. In theory, these methods can accurately control the conductance of the memristor. However, the voltage or current inputs required by these methods are too complex to be implemented, since irregular shape pulses are difficult to generate. For example, for the time-domain control [33], the input voltage curve requires an approximation using a 3rd, 4th, 7th, or 9th order function. Since generating that voltage consumes too much time and power, it is often impossible to realize at circuit level. Therefore, an effective solution that is not only suitable for most devices, but also simple enough to realize is desirable.

The third aspect is to utilize simply programmed pulses on memristors. Several programming schemes of the voltage pulse have been developed to achieve controllable conductance modulation. For example, the bipolar-pulse scheme [9, 34] applies a pair of positive and negative pulses with different amplitudes and durations. It partly mitigates nonlinearity at the low conductance stages where usually have large overshoots. However, the nonlinearity at the high conductance stages still exists. Also, in order to obtain precise conductance tuning, in [2, 35, 36], write-and-verify tuning with feedback circuits are used to adjust the device reliably. A linear and symmetric relation is demonstrated but using a much larger digital memory and multiple types of pulses [35]. With these methods, the conductance can be effectively controlled, but it needs to

identify and verify the precise conductance of the device for each weight update. Accordingly, extra processing circuits and a specific pulse generator are necessary, which increases the complexity of the circuit design and leads to area overhead and performance penalty.

In this research, a novel Piecewise Linearity (PL) method is proposed to address the nonlinearity problem for memristors. The proposed PL method, using the same amplitude pulses with simple duration adjustment and without identification and verification of the precise conductance, effectively mitigates the nonlinearity and achieves a high recognition accuracy in neuromorphic computing.

## 2.2. Related Work on Memristor-Based Neuromorphic Hardware Improvement for Privacy-Preserving Neural Network

With artificial neural networks (ANN) develops rapidly, it powers intelligent products by extracting patterns and building models. Meantime, data privacy greatly impacts our daily life, such as politics, security, businesses, relationships, health, and finances. The privacy problem is not limited to the threats associated with private data exposures or hacking attempts. It is also possible to glean extra information even if the data are anonymized and the ANN models are inaccessible. Privacy-preserving ANN technologies are proposed to make that ANN transform our society positively without risking our sensitive data, which is mainly conducted by cryptographic approaches or differential privacy approaches [37]. Especially, differential privacy, that is more efficient and popular, resists attacks by adding random noise to the input data, to iterations in a certain algorithm, or to the algorithm output. In 2017, the Google security and privacy team released a Private Aggregation via Teacher Ensembles (PATE) framework [38], which scales to learning tasks with large numbers of output classes and un-curated, imbalanced training data with errors, and it was proved as tighter differential-privacy guarantees. In 2018, the ARDEN

framework was proposed to protect the sensitive information via local differentially private and noise training [39]. However, because these technologies are all based on software technologies, the presentence of noise is bound to cause a drop in accuracy and it is impossible to get higher accuracy than that without noise injection. Also, software-based noise injection causes latency problems and computational overhead. Recently, designers proposed to exploit inherent noise with the equivalent error-prone hardware to replace software-based noise to save much power [40], which indicates the hardware can provide a more effective solution to realize privacy-preserving ANN.

In this research, instead of using traditional software method, we propose a method that applies in memristor-based ANN hardware system to improve privacy preserving space for differential privacy technology. The proposed method focuses on mitigating the nonlinearity problem of memristors to enable privacy preserving.

# 2.3. Related Work on Memristor Based Variation Enabled Differentially Private Learning Systems for Edge Computing in IoT

Most differentially private learning systems for IoT focus on algorithm-based framework improvement and optimization. For example, [41] proposes a framework that uses a protection layer to perform noise injection; and [42] designs a mechanism named LATENT that adds a randomization layer between the convolutional module and the fully connected module to perturb data for machine learning services. In [43], the Google security and privacy team released a Private Aggregation via Teacher Ensembles (PATE) framework that achieved private learning by carefully coordinating the activity of several different machine learning models. Differentially Private Stochastic Gradient Descent (DP-SGD) [44] makes fewer assumptions about the machine learning task than PATE, but it comes at the expense of making modifications to the training

algorithm. Such technologies inevitably need a large cost of noise-generation computing. Furthermore, all the above frameworks are software-based privacy protection technologies that might not be deployable on IoT devices due to resource constraints.

Other researchers have presented novel hardware level solutions. In [40], low-voltage static random-access memory (SRAM) chips are used to add bit failures as training data noise. This method can save energy, but the added noise only followed a uniform distribution, and does not guarantee DP. In [45, 46], in order to generate random numbers with true randomness, dedicated random number generation modules, such as physical unclonable function (PUF) and random number generator, are designed. These modules are accurate but require additional circuitry. In [47], an advanced neuro-morphic system is implemented based on memristor arrays, but noise is inserted in training data to promise strong theoretical privacy guarantees, where the hardware and software are utilized separately for learning and privacy protection.

Different from the above approaches, we propose a method that can achieve differentially private learning in edge AI with high efficiency and low computing cost by taking advantage of memristor-based hardware variations, which does not require any additional hardware or software. In this research, we utilize a 3-layer fully connected network and MNIST database as an example to verify the proposed method. However, our proposed method is generic, and can be applied to other databases and any deep learning models that can be mapped into a memristor-based crossbar array.

#### 3. PRELIMINARIES

This chapter provides preliminaries to this study by first introducing the concept of memristor, followed by discussing non-ideal properties of memristor. Second, besides discussing artificial neural networks (ANN), we also discussed how to build an ANN using memristors. Finally, a differential privacy concept is involved, which will provide the foundation for the rest of the dissertation.

#### 3.1. Artificial Neural Networks (ANN)

#### 3.1.1. Neural Networks

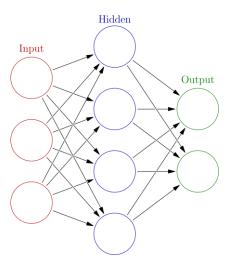

Artificial neural networks (ANNs), or neural networks (NNs), are computing systems inspired by the biological neural networks. An ANN is based on a collection of connected units or nodes called artificial neurons, which model the neurons in a biological brain. Each connection, like the synapses in a biological brain, can transmit a signal to other neurons. To be clear, in this research, such connection is named as synapses. An artificial neuron receives a signal then processes it by propagation function and produce weighted sum. This weighted sum is called activation. This weighted sum is then passed through a (usually nonlinear) activation function to produce the output. The initial inputs are external data, such as images and documents. The ultimate outputs accomplish the task, such as recognizing an object in an image. A given neuron can have multiple input and output connections. Between neurons, the weighted sum is passed to neighboring neurons that is connected by these connections (synapses). Each synapse also has a weight that adjusts as learning proceeds. The learning process of ANN is also called training process. Briefly, learning of ANN is a method by which a machine can extract information from data by sending it through different layers of abstraction. With learning process, we are teaching

an AI to recognize the differences between things like cats and dogs, and to find patterns in large amounts of data.

The three major learning paradigms are supervised learning, unsupervised learning and reinforcement learning. For supervised learning, the training of a neural network from a given example is usually conducted by determining the difference between the processed output of the network (often a prediction) and a target output. This difference is the error. The network then adjusts its weighted associations according to a learning rule and using this error value. Successive adjustments will cause the neural network to produce output which is increasingly similar to the target output. After a sufficient number of these adjustments the training can be terminated based upon certain criteria. For unsupervised learning, take image recognition as an example, developers create algorithms that cluster data by similarities. Instead of trying to determine if a group of pixels is cat or a dog, for example, it simply tries to figure out everything it can be. It output patterns in clusters and is possible to separate the images into dogs, cats, brown animals, white animals and so on. For reinforcement learning, the aim is to weight the network (devise a policy) to perform actions that minimize long-term (expected cumulative) cost.

Some hyperparameters needs to be set before the learning process begins. Examples of hyperparameters include learning rate, the number of hidden layers and batch size. The learning rate defines the size of the corrective steps that the model takes to adjust for errors in each training step. A high learning rate shortens the training time, but with lower ultimate accuracy, while a lower learning rate takes longer, but with the potential for greater accuracy. A cost function is a mathematical formula used to evaluate how production expenses will change at different output levels. In other words, it estimates the total cost of production given a specific quantity produced. Backpropagation is a method used to adjust the connection weights to compensate for each error

found during learning. The error amount is effectively divided among the connections. Technically, backprop calculates the gradient (the derivative) of the cost function associated with a given state with respect to the weights. The weight updates can be done via stochastic gradient descent or other methods.

In this section, we take a three-layer neural network as an example to illustrate the machine learning process. An artificial neural network is an interconnected group of nodes, inspired by a simplification of neurons in a brain. Here, each circular node represents an artificial neuron, and an arrow represents a connection from the output of one artificial neuron to the input of another.

Figure 1. Artificial neural network.

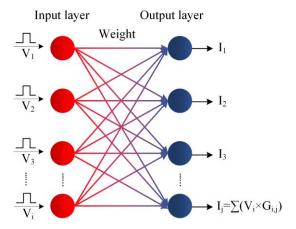

Figure 2. Neural network between two layers.  $V_i$ ,  $G_{i,j}$ , and  $I_j$  represent the input signal in  $i^{th}$  neuron, the weight of the synapses in  $j^{th}$  neuron of output layer and  $i^{th}$  neuron in input layer, and the output sum that represent the dot product result of V and G, respectively.

#### 3.1.2. SGD Algorithm

Stochastic gradient descent (often abbreviated SGD) is an iterative method for optimizing an objective function. It can be regarded as a stochastic approximation of gradient descent optimization, since it replaces the actual gradient (calculated from the entire data set) by an estimate thereof (calculated from a randomly selected subset of the data). Especially in high-dimensional optimization problems this reduces the computational burden, achieving faster iterations in trade for a lower convergence rate.

$$Q(w) = \frac{1}{n} \sum_{i=1}^{n} Q_i(w)$$

(1)

where the parameter w that minimizes Q(w) is to be estimated. Each summand function  $Q_i$  is typically associated with the i-th observation in the data set (used for training).

When used to minimize the above function, a standard (or "batch") gradient descent method would perform the following iterations.

$$w = w - \frac{\eta}{n} \sum_{i=1}^{n} \nabla Q_i(w) \tag{2}$$

where  $\eta$  is a step size (sometimes called the learning rate in machine learning).

#### 3.1.3. Long-term Potentiation (LTP) and Long-term Depression (LTD)

Long-term potentiation (LTP) and long-term depression (LTD) are cellular processes involved in learning and memory. In this research, the terms LTD and LTD are used to represent the trend of each synapse weight change. In other words, it represents the trend of each memristor conductance change for each synapse. Concretely, the conductance of the memristor (*G*) represents the weight of the synapse and it needs to be updated frequently during the data training process as determined by learning algorithms. In such updating process, the conductance can either increase in a process as long-term potentiation (LTP) or decrease in a process as long-term depression (LTD). In other words, the process that the stimulation leads to a persistent increase of the weight is called long-term potentiation of synapses, or LTP for short. The process that the stimulation leads to a persistent decrease of the weight is called long-term depression (LTD), or LTD for short. Ideally, when LTP or LTD occurs, the change in the conductance of an ideal synapse device is proportional to the number of input pulses.

#### 3.2. Memristors

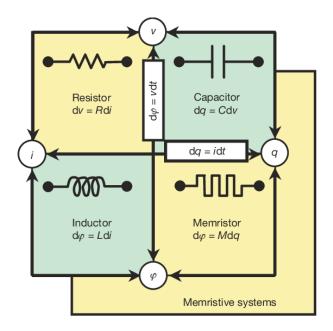

A memristor is an analog device to exploit the multilevel conductance states, to regulate the flow of electrical current, and to store the amount of charge that has previously flowed through it [4, 5]. It can realize desirable device properties such as sub-10 nm feature sizes [7], sub-nanosecond switching speed [8, 9], long write-erase endurance [17], and nanoamperes programming energy [18].

Memristor is name from memory and resistor. The concept of the memristor was first proposed by Chua. Memristor is introduced as the fourth hidden fundamental element, in addition to the resistor, inductor, and capacitor. The theoretical memristor connects the flux  $\varphi$  and charge q, which is shown in the equation:  $d\varphi = Md(q)$  [5].

Figure 3. The four fundamental two-terminal circuit elements.

In 2008, Hewlett-Packard researchers presented the prototypical memristor (memory + resistor) devices based on a titanium dioxide insulator layer sandwiched between two metal electrodes (2008). The insulator layer comprises of a stoichiometric titanium oxide layer and a non-stoichiometric titanium sub-oxide layer (TiO<sub>2</sub>/TiO<sub>2-x</sub>). This prototypical device's conductance can be changed by applying a voltage bias across the Pt electrodes. Such ability of encoding the biasing history makes the memristor be a promising storage memory. Different from dynamic random-access memory (DRAM) or static random-access memory (SRAM), memristors can realize non-volatile property, sub-10 nm feature sizes [12], sub-nanosecond switching speed [13, 14], long write-erase endurance [15], and nanoamperes programming energy [16]. However, it is challenged to combine all these properties into a single material system.

Also, different from digital conductance change, the analog conductance tunability of memristor makes in-memory computing be possible. Unlike existing CMOS-based memory technology, which reads volatile capacitance states, memristor technology is a nonvolatile

technology that stores data using nonvolatile resistance states. All these devices exhibit an I-V hysteresis that changes from low resistance states (LRSs) to high resistance states (HRSs) and vice versa. Moreover, the area surrounded by the I-V hysteresis loop is continuously changed by changing the applied electrical signal. In other words, the memristor implements gradual conductance changes that can be utilized as synaptic plasticity.

As a result, it can not only act as the non-volatile memory, but realize the in-memory calculation which brings high potential to implement neural networks in hardware [3]. In-memory or near-memory computing with SRAM, DRAM, or flash memory provides a highly parallel solution to resolve the 'memory wall' of the von-Neumann architecture.

#### 3.2.1. Synaptic Device

Since memristor fabricated by HP in 2008, most memristors are built using simple three-layer structures consisting of two electrodes layer and a switching layer that is generally comprised of dielectrics. The dielectrics used are mainly binary oxide materials such as silicon oxide (SiO2), titanium oxide (TiO2), copper oxide (CuO), nickel oxide (NiO), zinc oxide (ZnO), hafnium oxide (HfO2), tantalum oxide (Ta2O5) and aluminum oxide (Al2O3). Depending on the material and structure of memristors, the resistive switching characteristics can either be abrupt (binary) or gradual (analog). The abrupt resistance change is suitable for storing or processing binary data, and the gradual resistance change is more suitable for storing multiple resistance states for analog computing. There are reports of other switching materials, including heterogeneous materials, such as phase change memory (PCM) that are mainly built out of Chalcogenide materials (prime example is Ge2Sb2Te5). The other switching materials are cerium oxide and strontium Titanate (CeO2 and SrTiO3); organic materials, such as copper-Tetracyanoquinodimethane (Cu-TCNQ); electrolytic materials, such as copper sulfide (Cu2S) and chalcogenides such as silver—germanium—

selenium (Ag-Ge-Se). However, because of the unconventional fabrication techniques, CMOS compatibility issues, or relatively unstable physical characteristics, these materials are less commonly used.

In this research, we focus on implementing artificial neural network that generally consists of a large number of synapses. Memristor with gradual resistance change is more suitable for storing multiple resistance states for analog neural computing that implements the function of Sum of Product (SOP). Therefore, in this research, the synaptic devices that we adopted for neuromorphic computing is the memristor with gradual (analog) resistance change. For the rest of this dissertation, all mentioned memristors are refer to a special subset of the resistive memory devices that can continuously tune the conductance into multi-level states.

In a memristor-based neuromorphic computing platform, memristors are connected as neuron devices that implement the function of the Sum of Product (SOP). Weight update depends on the transition between different conductance states in memristors, which is typically triggered by voltage pulses. Specifically, according to the programmed voltage pulses, the conductance of memristors positively and negatively changes, enabling weight increase and decrease, respectively [3]. However, memristors are not flawless and intrinsically suffering from their variability issues. The physical mechanism of the conductance modulation in most prospective synaptic devices is typically an ionic reconfiguration process based on electro/thermo-dynamics [7, 8]. This atomic-level random process is responsible for unavoidable variations including nonlinearity, device-to-device, cycle-to-cycle, and ON/OFF conductance variations [9]. We discuss nonlinear property and cycle-to-cycle variation in the following sub-sections.

# 3.2.2. Nonlinearity of Memristors

The conductance of the memristor (G) represents the weight of the synapse and it needs to be updated frequently during the data training process as determined by learning algorithms. In such updating process, the conductance can either increase in a process as long-term potentiation (LTP) or decrease in a process as long-term depression (LTD), as shown in Figure 4 (a). Ideally, when LTP or LTD occurs, the change in the conductance of an ideal synapse device is proportional to the number of input pulses. Unfortunately, in reality, such change mismatches the input pulse due to the nonlinearity of memristors. For instance, as demonstrated in Figure 4 (b), the curve (black) represents the conductance of an actual memristor device as a function of the number of input pulses where the pulses have the same duration and the same amplitude. While the line (red) in Figure 4 (b) represents the function of the ideal case. In LTP, as shown in Figure 4 (b), assuming in a weight update process, the device's conductance needs to be updated from point a to b. Usually, the corresponding number of pulses is calculated according to the ideal case (red). But, when these pulses are applied to the actual device, instead of changing from point a to b, the device conductance changes from point a to c. Therefore, the actual change of conductance and the required change are quite different. Similar weight updating error occurs in the LTD process. Consequently, the nonlinearity of the memristor causes the weight change of the synapse device to be inconsistent with the change required by the learning algorithm, thereby reducing the accuracy of ANN's recognition.

Figure 4. The conductance change (weight updating) curve. (a) Conductance changes with identical input pulses. (b) Weight updating process based on linear line. (c) Weight updating process based on a piecewise line.

We adopt a general conductance change behavior model [9] that is defined by the following equations:

$$G_{LTP} = B \left( 1 - e^{\left( -\frac{P}{A} \right)} \right) + G_{min} \tag{3}$$

$$G_{LTD} = -B \left( 1 - e^{\left( -\frac{P - P_{max}}{A} \right)} \right) + G_{max}$$

(4)

$$B = \frac{G_{max} - G_{min}}{1 - e^{\left(\frac{-P_{max}}{A}\right)}} \tag{5}$$

where  $G_{max}$ ,  $G_{min}$ , and  $P_{max}$  are directly extracted from the actual test data [9], which represents the maximum conductance, minimum conductance, and the maximum pulse number required to switch the device between the minimum and maximum conductance states. A and B are the parameter that controls the nonlinear behavior of the weight update. In this model, by adjusting A, the conductance curve is labeled with a nonlinearity value (NL) from +6 to -6, which represents the extent to the curve deviates from the ideal linear device and is illustrated in Figure 5. Here the positive (+) and negative (-) signs are merely to label LTP and LTD, respectively.

Figure 5. Conductance change curves under various nonlinearity of LTP and LTD.

# 3.2.3. Cycle-to-cycle Variation of Memristors

Memristors can achieve multiple conductance states. In our learning system, the conductance of each memristor represents the weight of each synapse. As shown in Figure 6, positive and negative input voltage pulses that are larger than the threshold voltage can switch a memristor gradually from Gmin to Gmax or from Gmax to Gmin, where Gmin and Gmax represent minimum conductance and maximum conductance, respectively. Thus, the conductance/weight increase process is called long-term potentiation (LTP) and the conductance/weight decrease process is called long-term depression (LTD) [48].

In the backpropagation phase of the DP-SGD algorithm, the weight update values ( $\Delta w$ ) will be translated to a number of LTP or LTD pulses and applied to the synaptic array. The amount of conductance change should be linearly proportional to the number of write pulses; however, this linear change is broken by memristor variations. Among all variations of memristors not attributed to manufacturing process, cycle-to-cycle variation is caused by intrinsically stochastic resistance switching mechanisms [49-52] that can be approximated as a Gaussian or normal distribution [45, 46, 53-57]. It originates from the random formation and disruption of conducting

filaments [51] and the co-existence of multiple sub-filaments, where the active, current-carrying filament may change from cycle to cycle [52, 58]. To prove such randomness introduced by each programming operation, 500 cycles [59] and 5000 cycles [56] of experimental data are collected. Cycle-to-cycle variations result in the different updated conductance when the same updating signal in different updating cycles is applied to a memristor, even when the initial conductance is the same.

Figure 6. Long-term potentiation process (LTP), long-term decrease process (LTD), and cycle-to-cycle variation of a memristor.  $N_{\text{Level}}$  represents the number of conductance states of a memristor.

#### 3.2.4. Artificial Neural Networks (ANN) and Memristor

ANN are computing systems vaguely inspired by the biological neural networks that transform inputs to desired outputs by feed-forward networks. As shown in Figure 7, each neuron in the network takes a weighted sum of the outputs of the prior layer, and then transfer the sum to the next layer.

In the hardware implementation, the neural network can be directly mapped into a crossbar from where the inputs are connected into the rows and the outputs are connected into the columns.

Memristor-based crossbar circuit can store the synaptic weight and calculate the desired result (Sum of Product), at the same time, extremely improving the system efficiency. The desirable properties of memristors support the memristor-based crossbar circuit to be a promising substitute technology to traditional ones so that researchers begin realizing device-engineering and array-integration hardware implementation of memristors. Usually, as shown in Figure 7, in the hardware application of the neural network, memristors act as synapses in crossbar structure and locate in each cross point.

Figure 7. Hardware implementation of neural networks using memristor crossbar.  $V_i$ ,  $G_{i,j}$ , and  $I_j$  represent the input signal in i<sup>th</sup> row, the conductance of the memristor in j<sup>th</sup> column and i<sup>th</sup> row, and the output current that represent the dot product result of V and G, respectively.

Figure 8. Block diagram of circuit flow of a three-layer ANN.

# 3.3. Differential Privacy